# Layered Manufacturing

Thin Film Processes: MEMS and Microelectronics

1

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

2

### 2.008 Coverage

#### Thin Film Processes

MEMS

Microelectronics

Surface Coating

Layered Composites Manufacturing

Additive Manufacturing

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

3

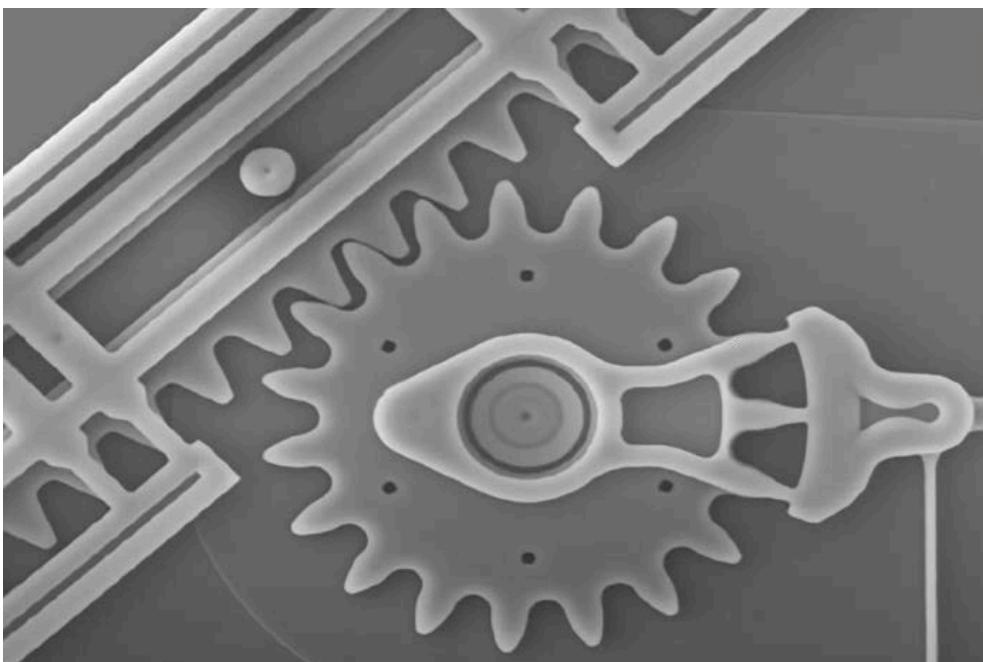

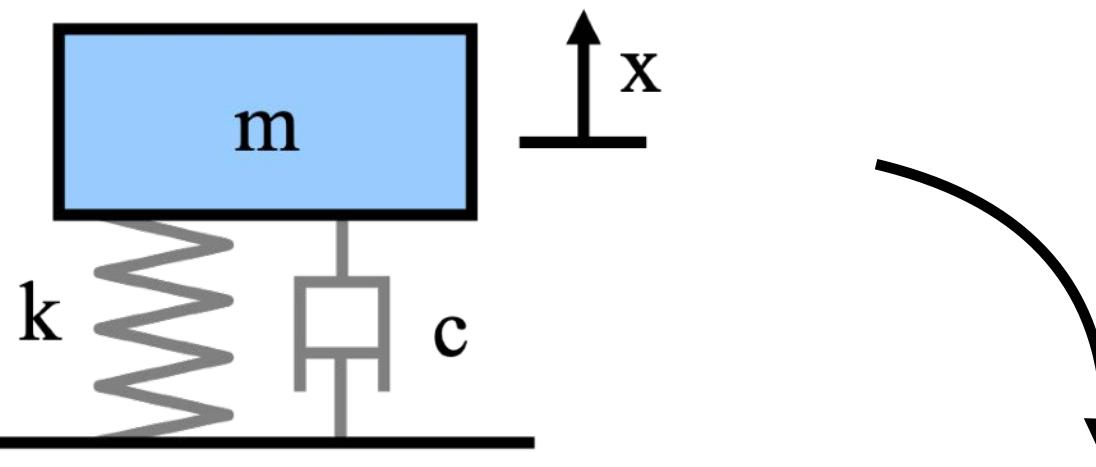

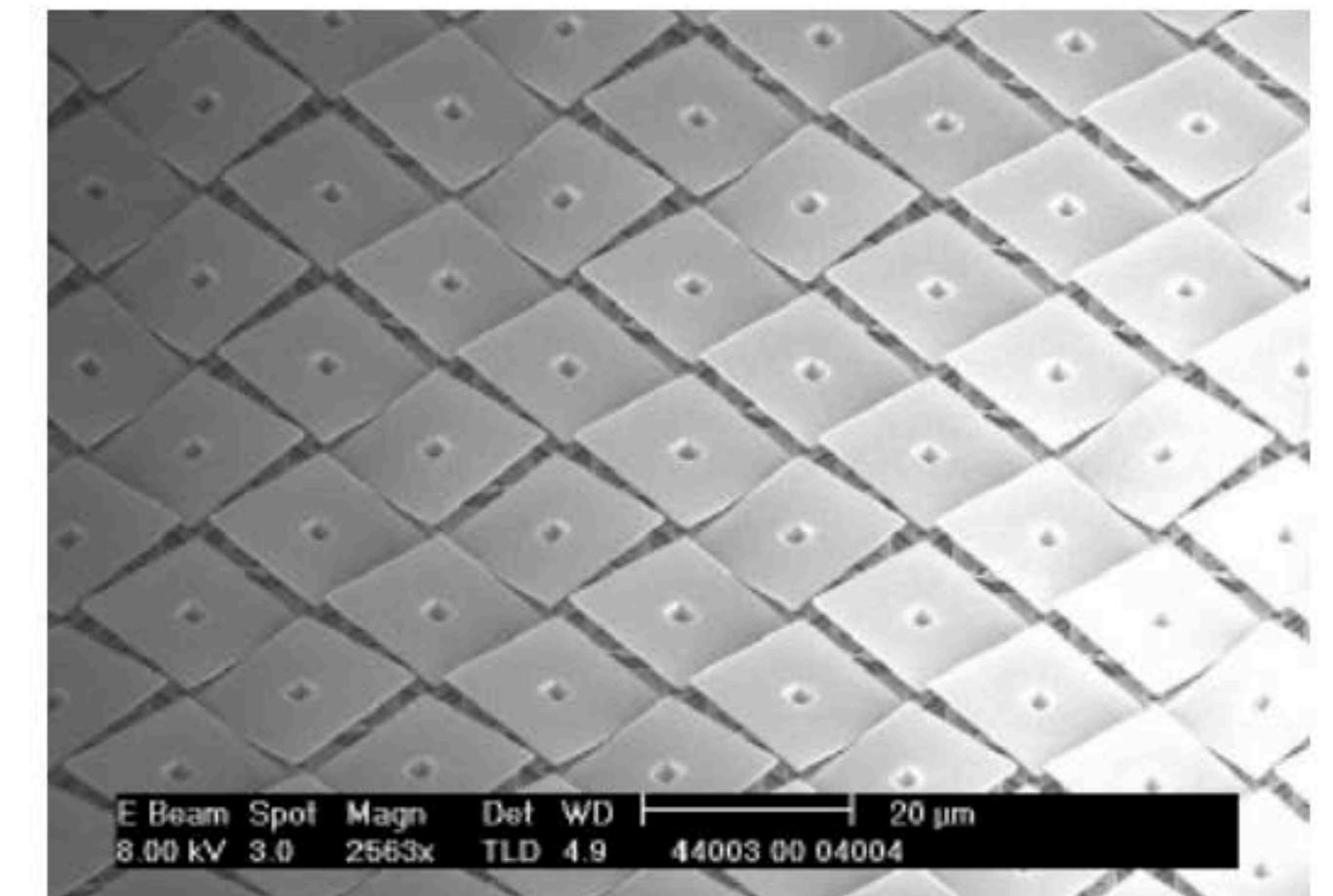

### MEMS: Micro-electromechanical Systems

- $\mu\text{m}$  scale: small but mighty

- integrated systems of sensing, actuation, communication, control, power and computing

- **low power**

- **low cost**

- rapidly developing field: chemical, bio, fluidic, optical, pharma

Accelerometers

- airbags: low cost allows for **democratization** of technology

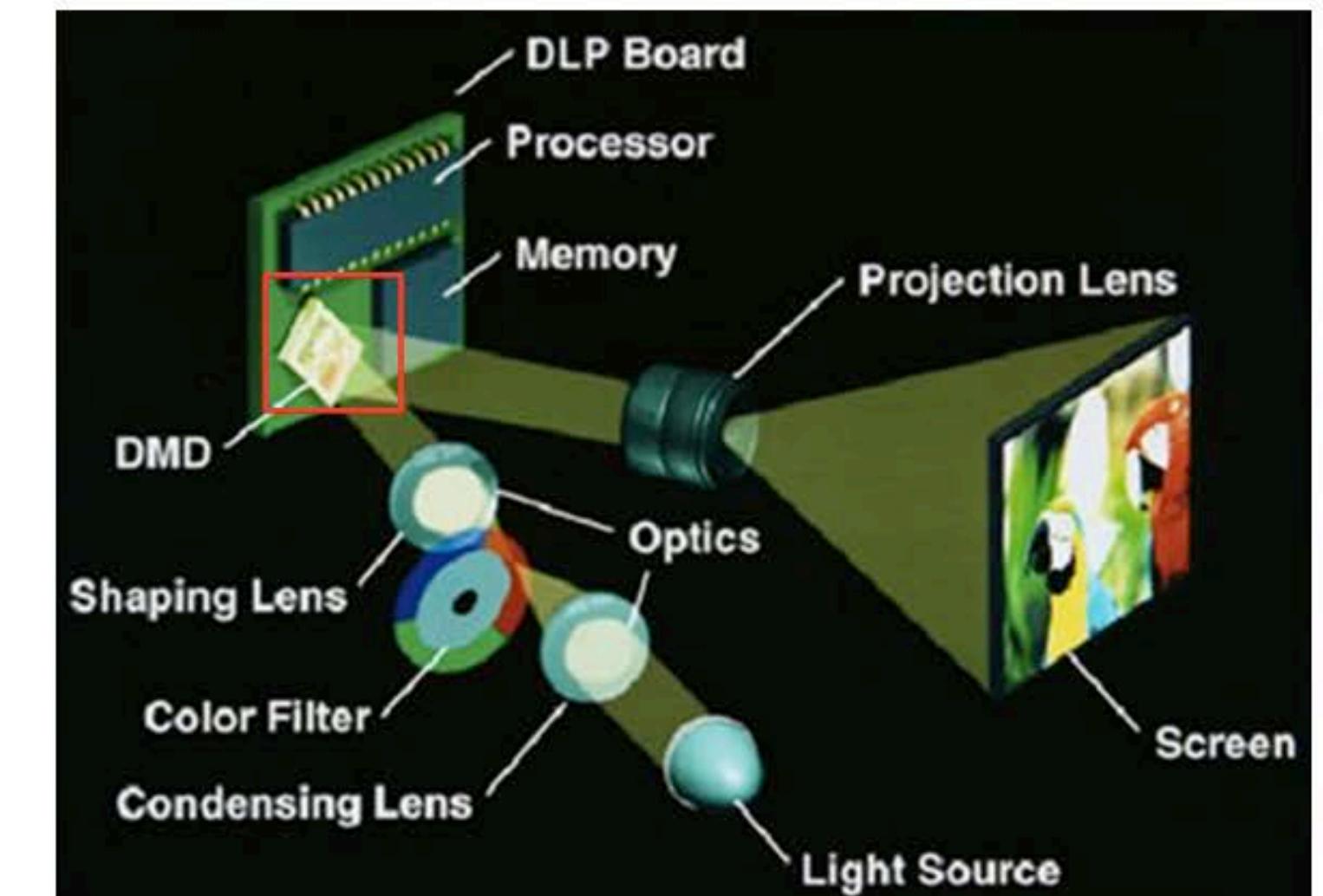

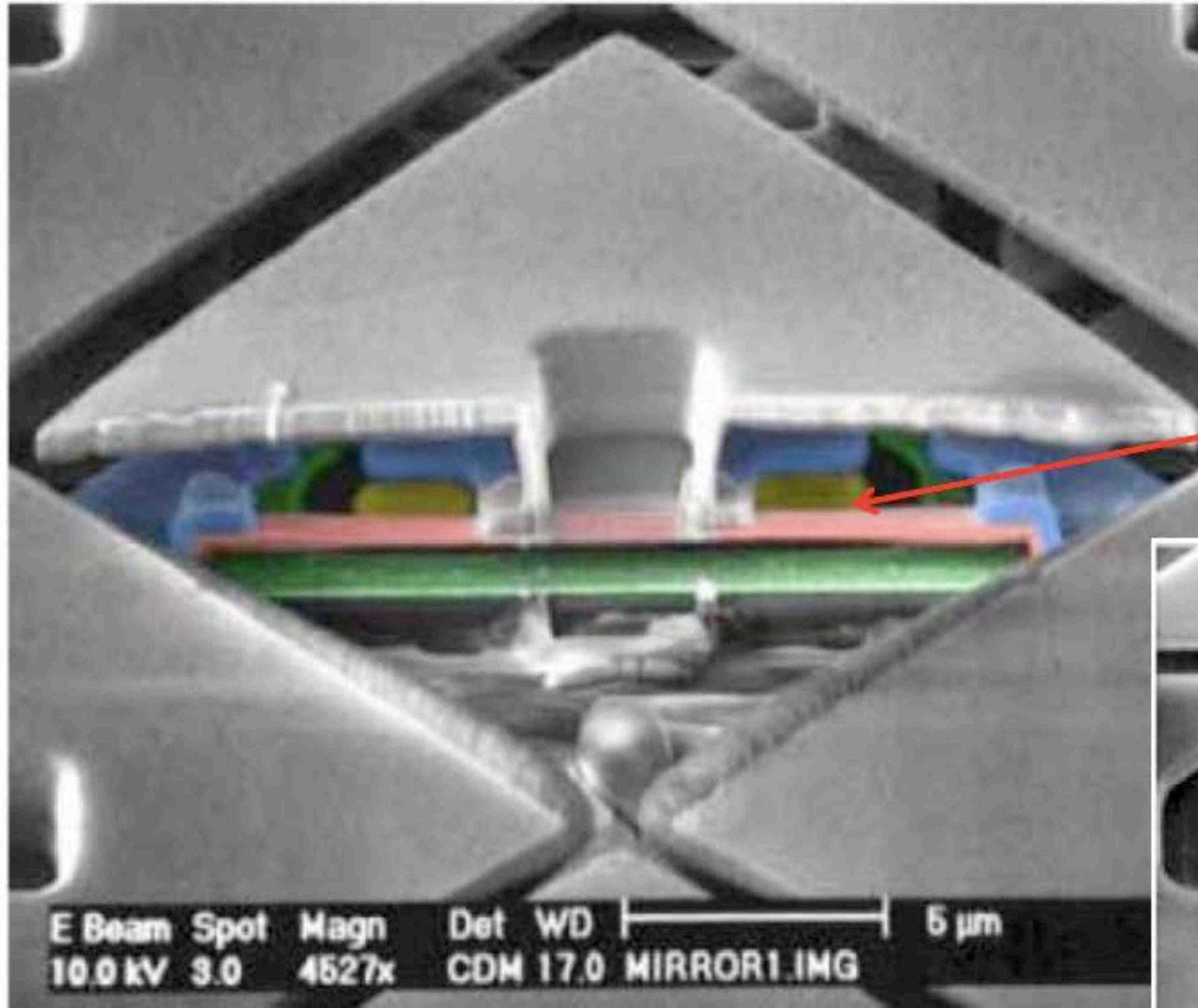

DMD (Digital Micromirror Device) for DLP (Digital Light Processing)

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

4

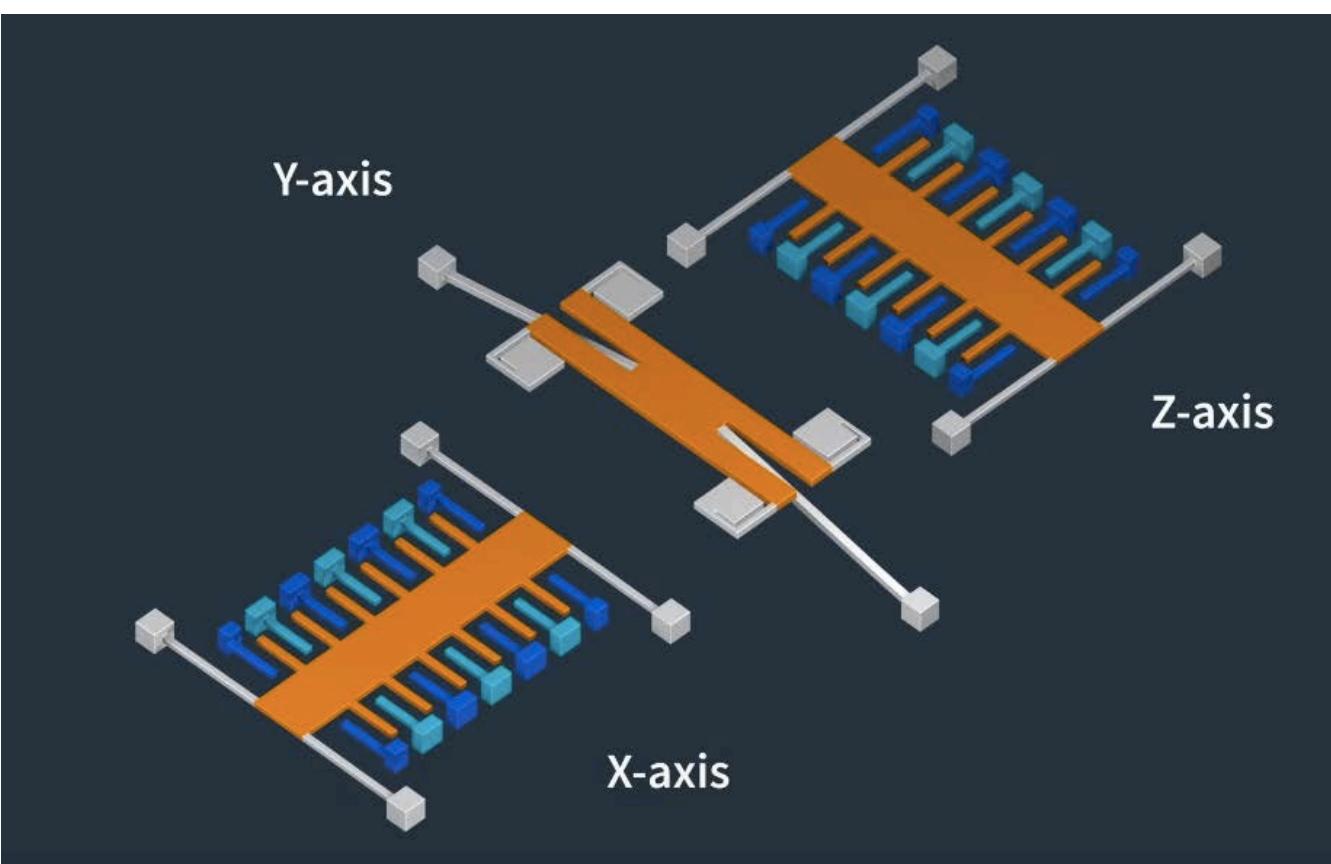

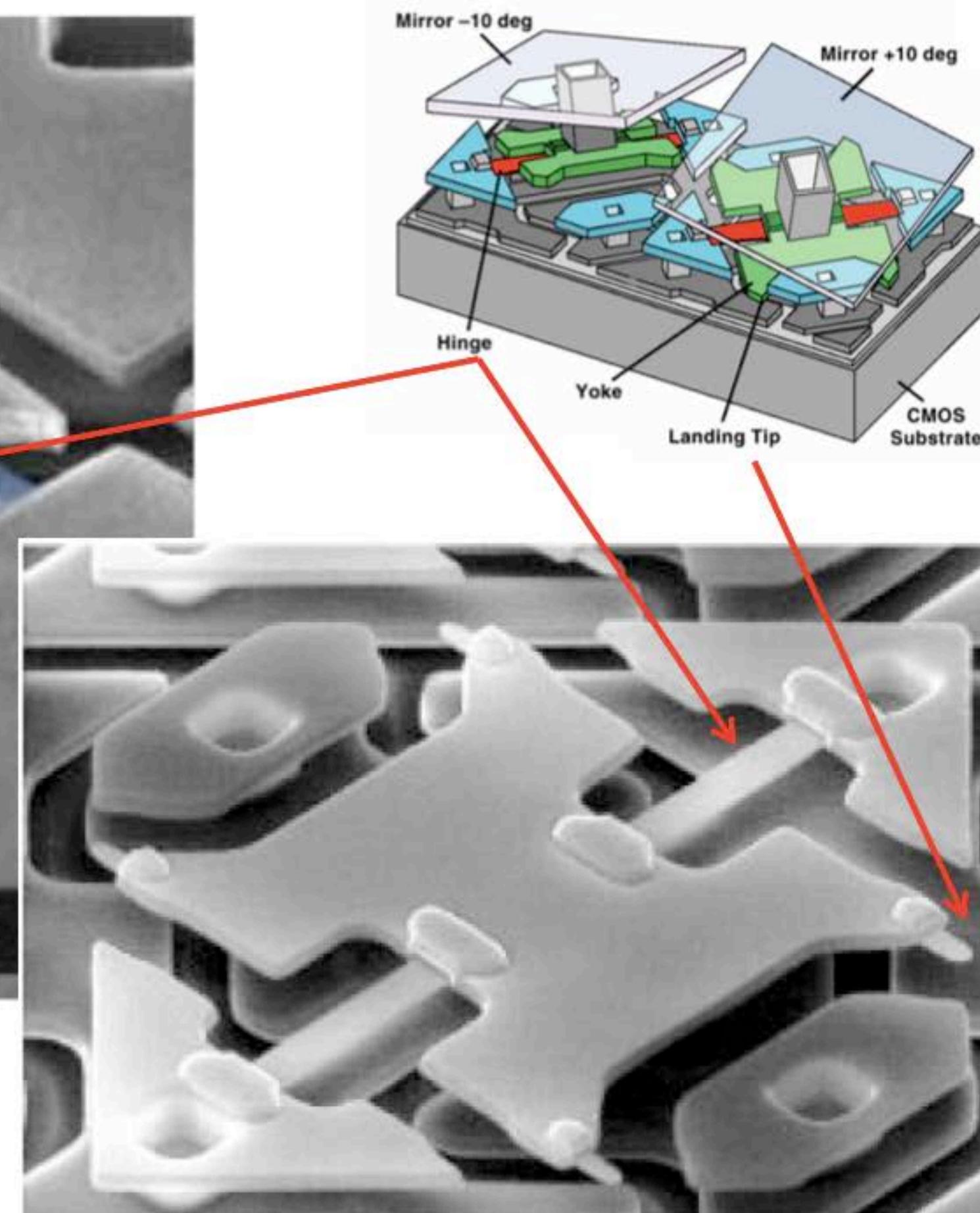

### MEMS: Micro-electromechanical Systems

2000 x 1000 = 2 million mirrors!

each mirror  $5 \times 5 \mu\text{m}$ !

fatigue life:  $10^{12}$  cycles!

DMD (Digital Micromirror Device) for DLP (Digital Light Processing)

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

5

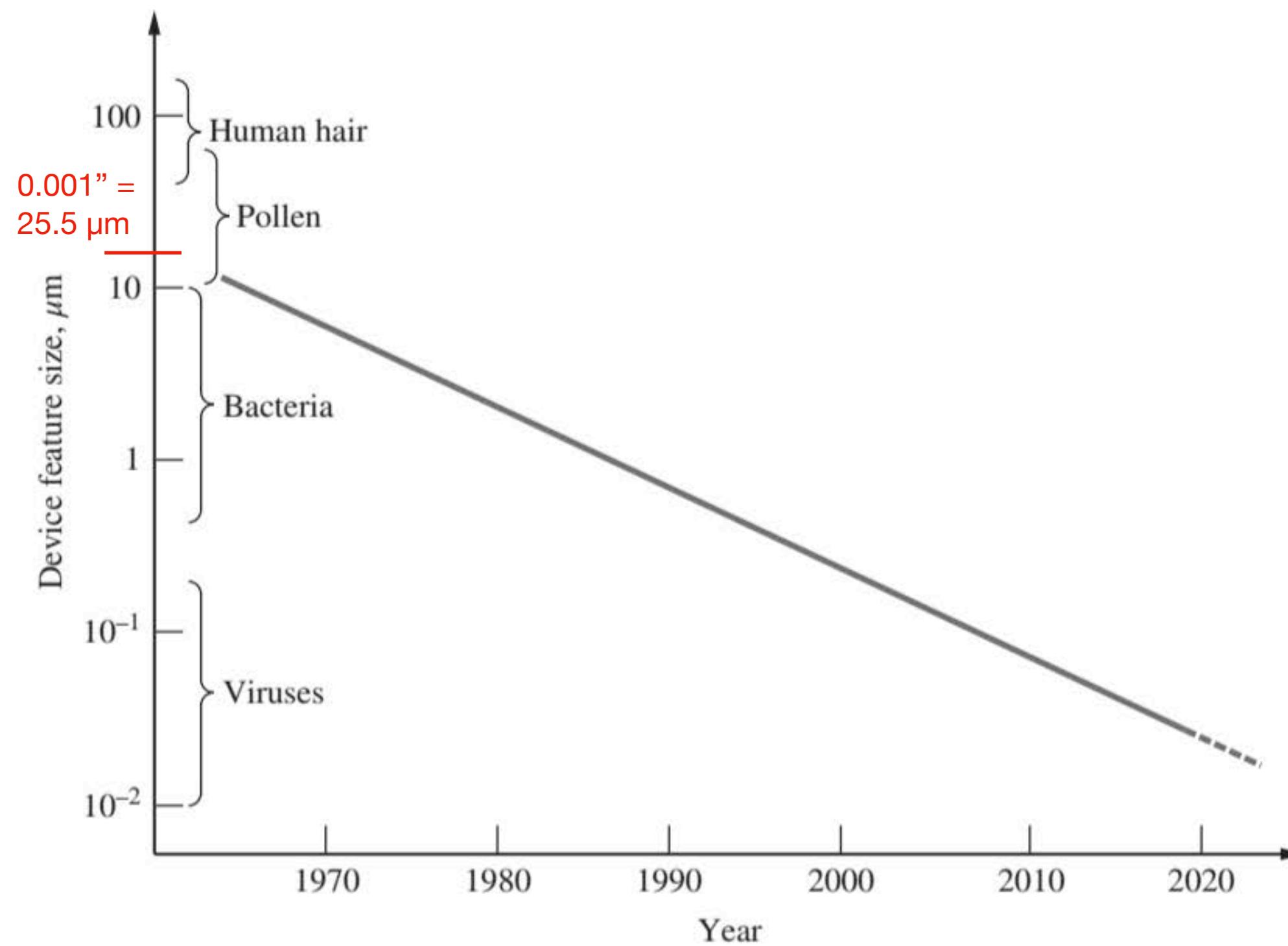

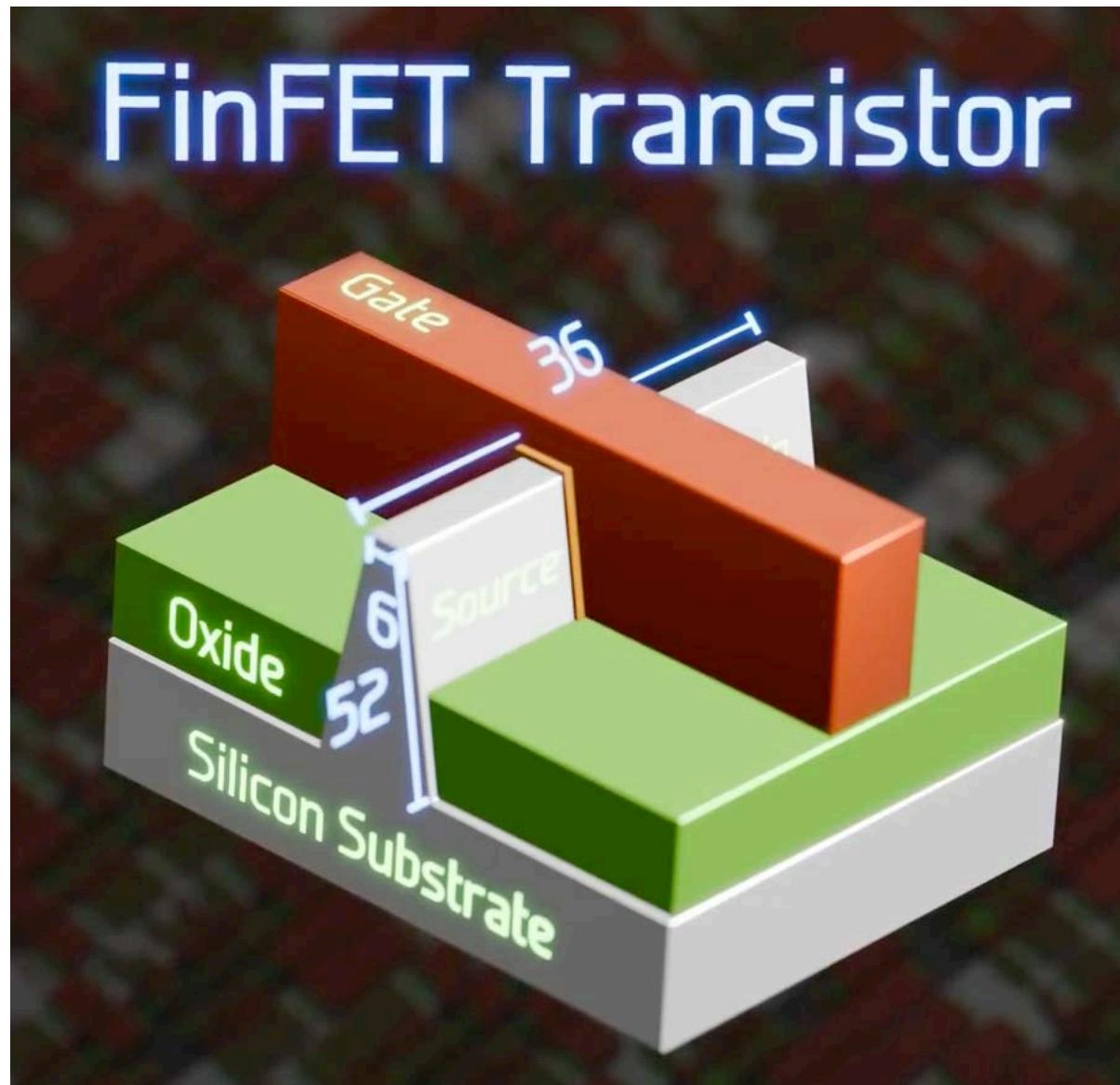

### Micro-electronic Devices

increase in performance compared to “macro” technologies while decreasing cost

- what's the **downside**?

- **huge investment** in technology and manufacturing processes to get economy of scale

0.03 vs 0.02 ¢/hour

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

6

### Manufacturing Across Scales

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

7

### Manufacturing Across Scales

sizes in [nm]

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

8

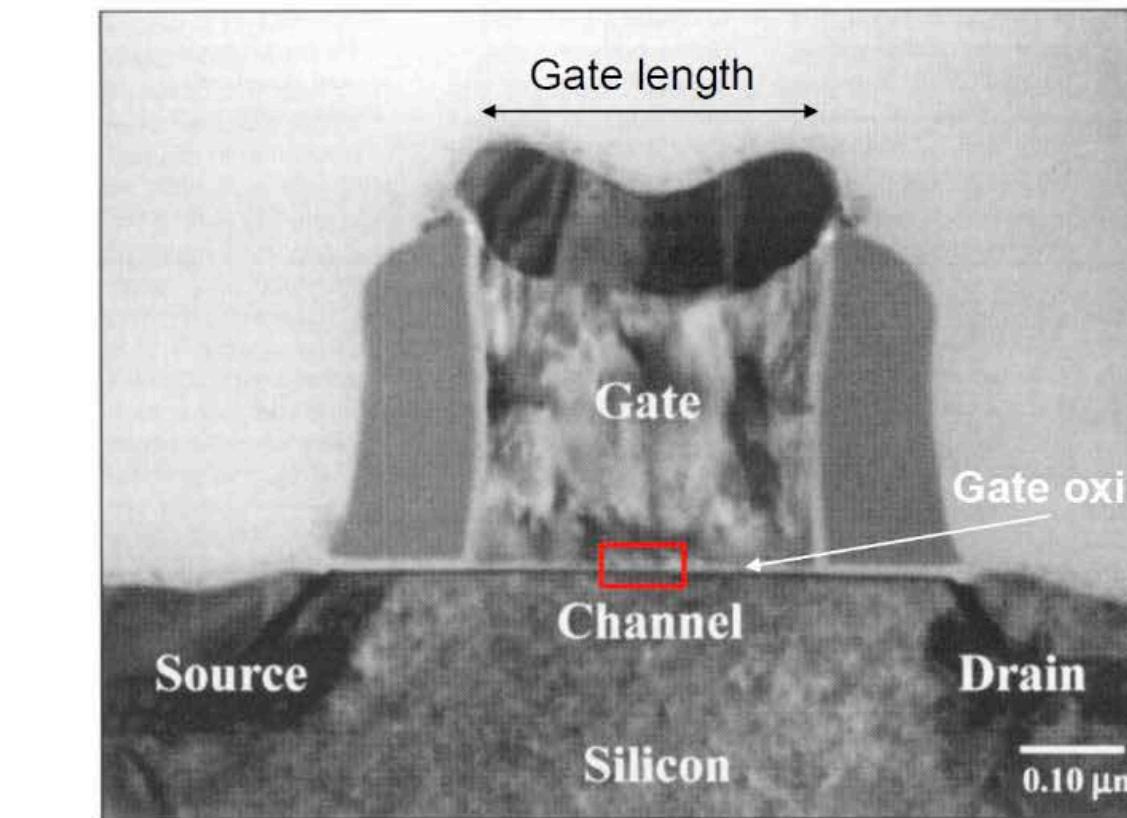

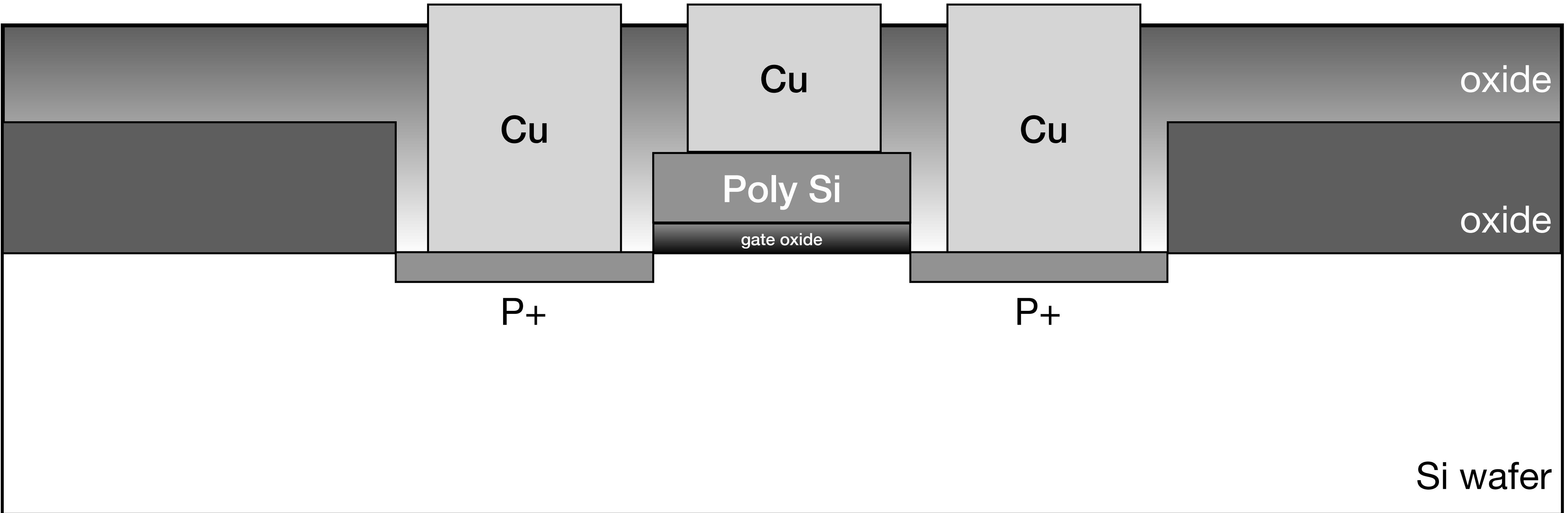

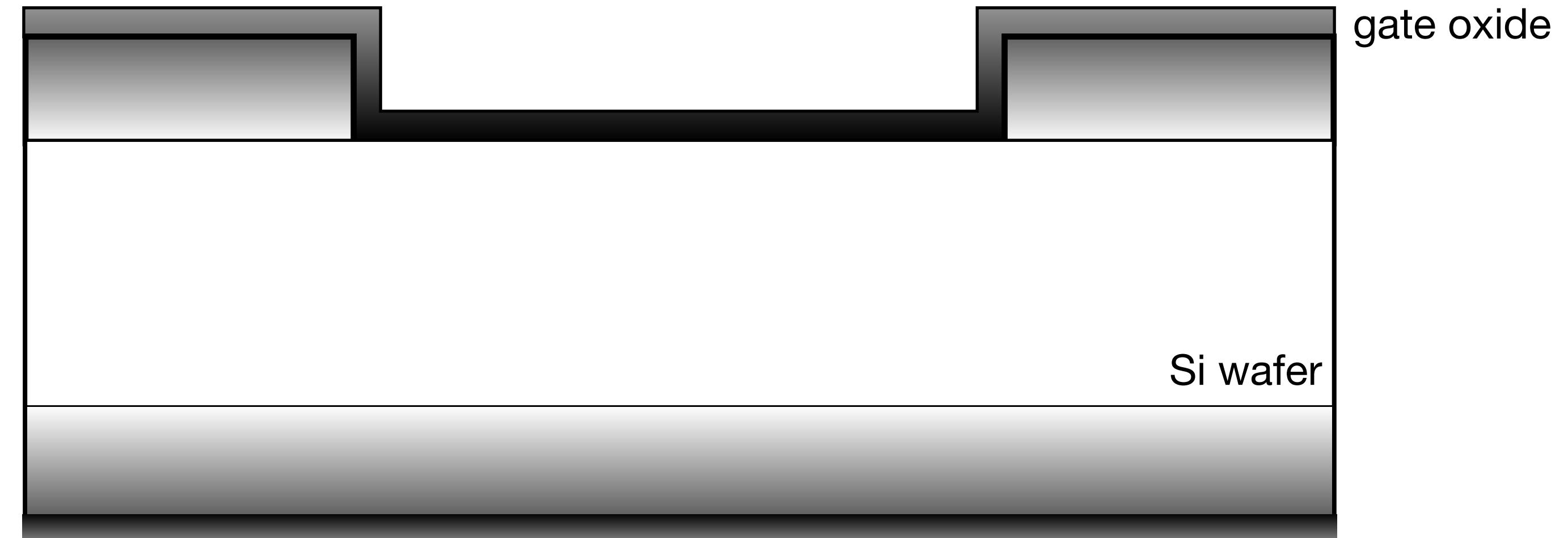

### Microelectronics Fabrication

### PMOS Transistor

- typical mechanical engineering assembly?

# Layered Manufacturing

Thin Film Processes: MEMS and Microelectronics

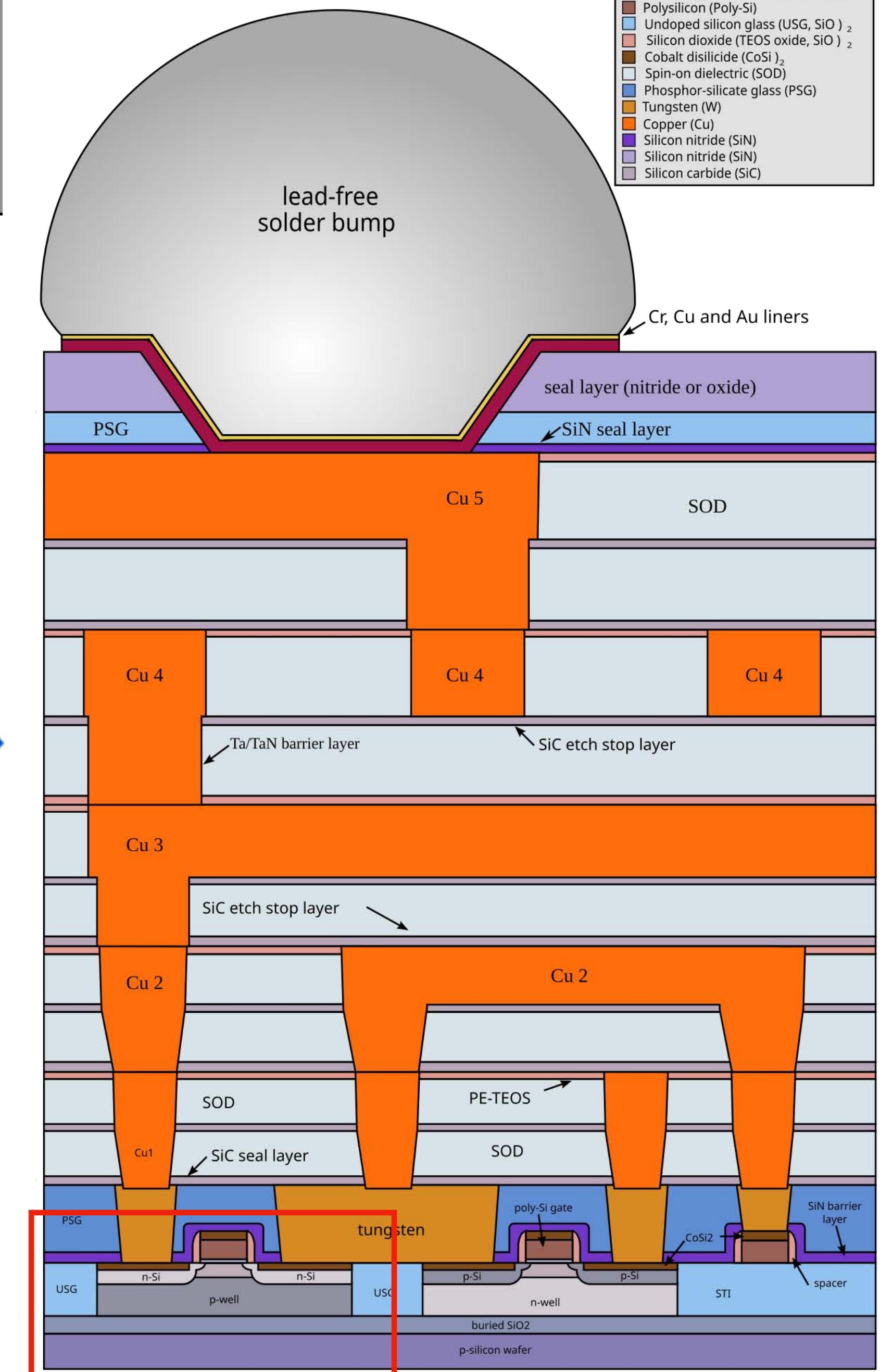

Legend:

|                                               |      |      |

|-----------------------------------------------|------|------|

| Silicon (Si)                                  | n-Si | p-Si |

| Polysilicon (Poly-Si)                         |      |      |

| Undoped silicon glass (USG, $\text{SiO}_2$ )  |      |      |

| Silicon dioxide (TEOS oxide, $\text{SiO}_2$ ) |      |      |

| Cobalt disilicide ( $\text{CoSi}_2$ )         |      |      |

| Spin-on dielectric (SOD)                      |      |      |

| Phosphor-silicate glass (PSG)                 |      |      |

| Tungsten (W)                                  |      |      |

| Copper (Cu)                                   |      |      |

| Silicon nitride (SiN)                         |      |      |

| Silicon nitride (SiN)                         |      |      |

| Silicon carbide (SiC)                         |      |      |

9

## Microelectronics Fabrication

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

10

### PMOS Transistor

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

11

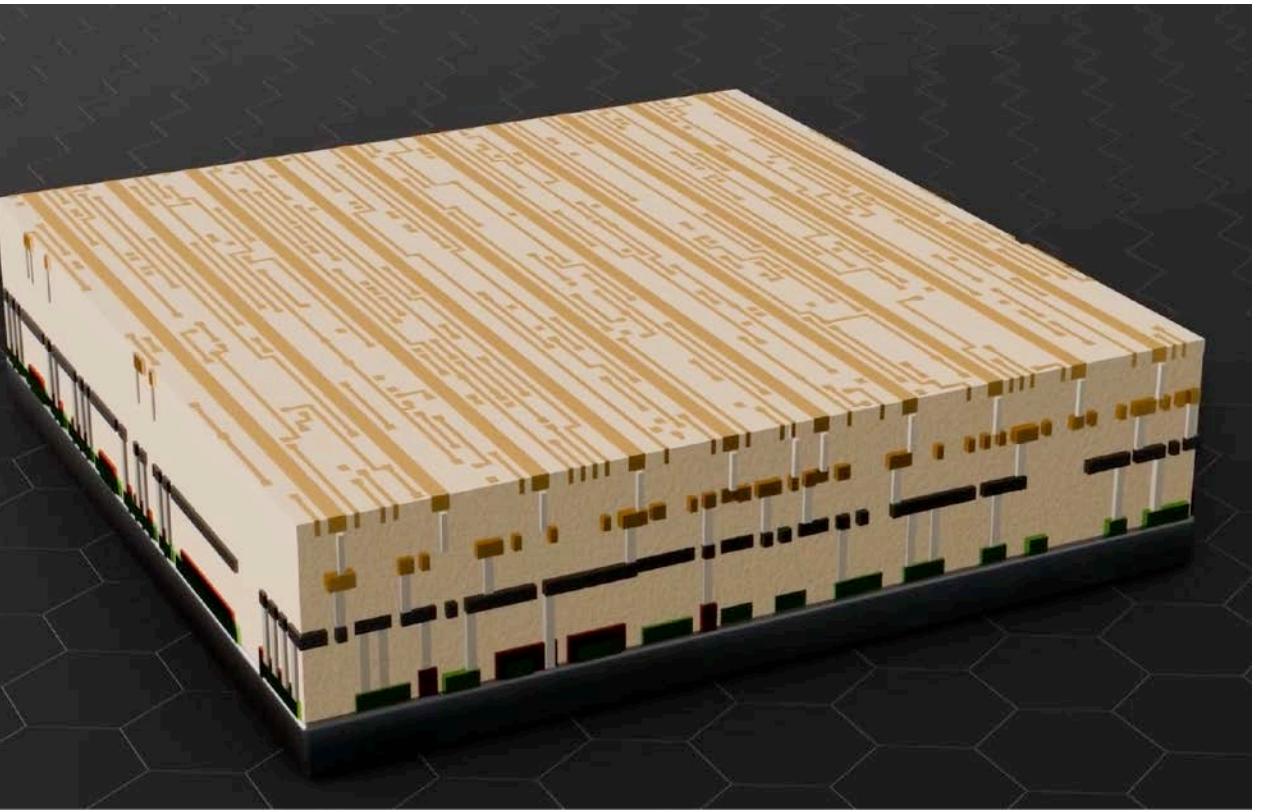

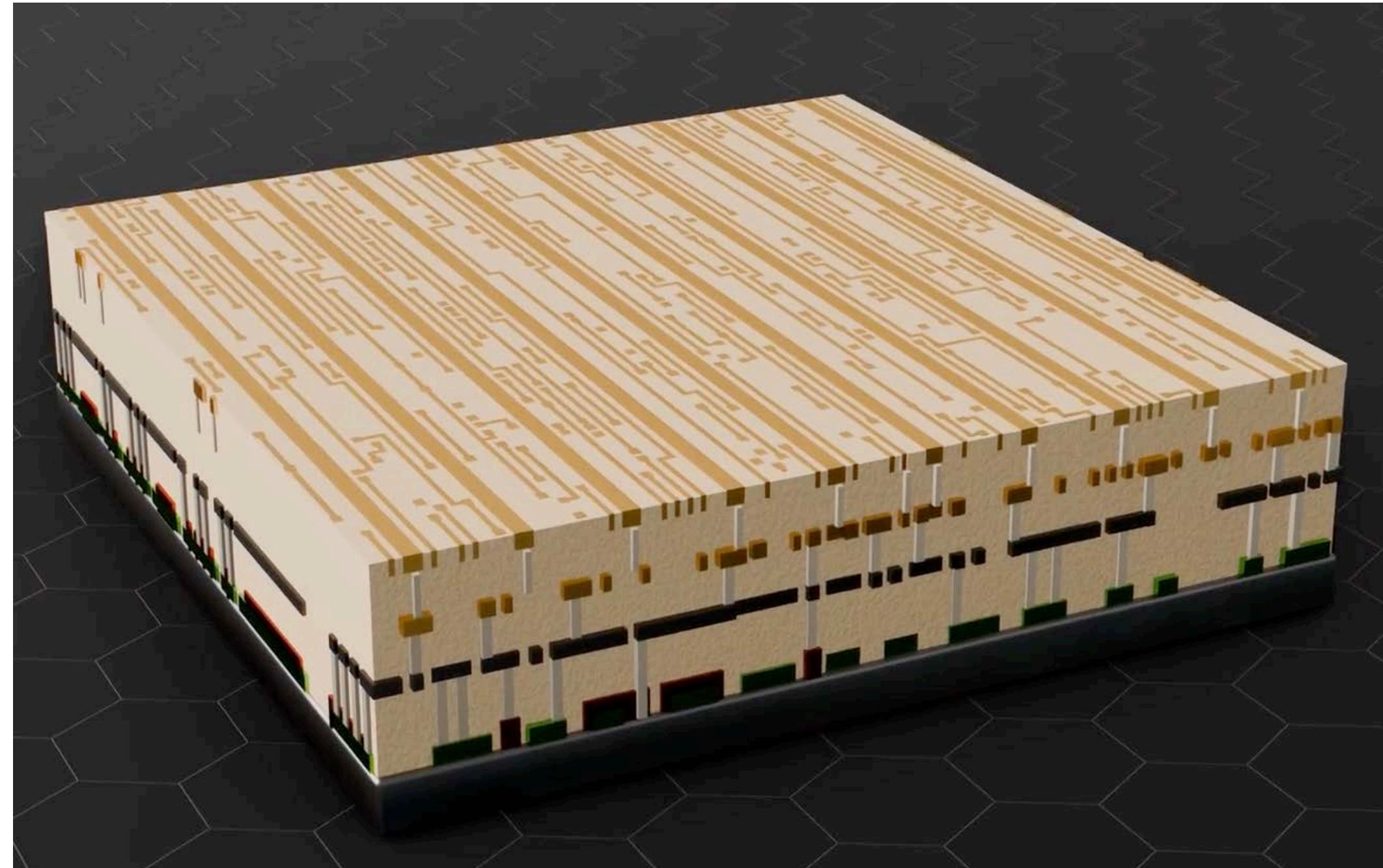

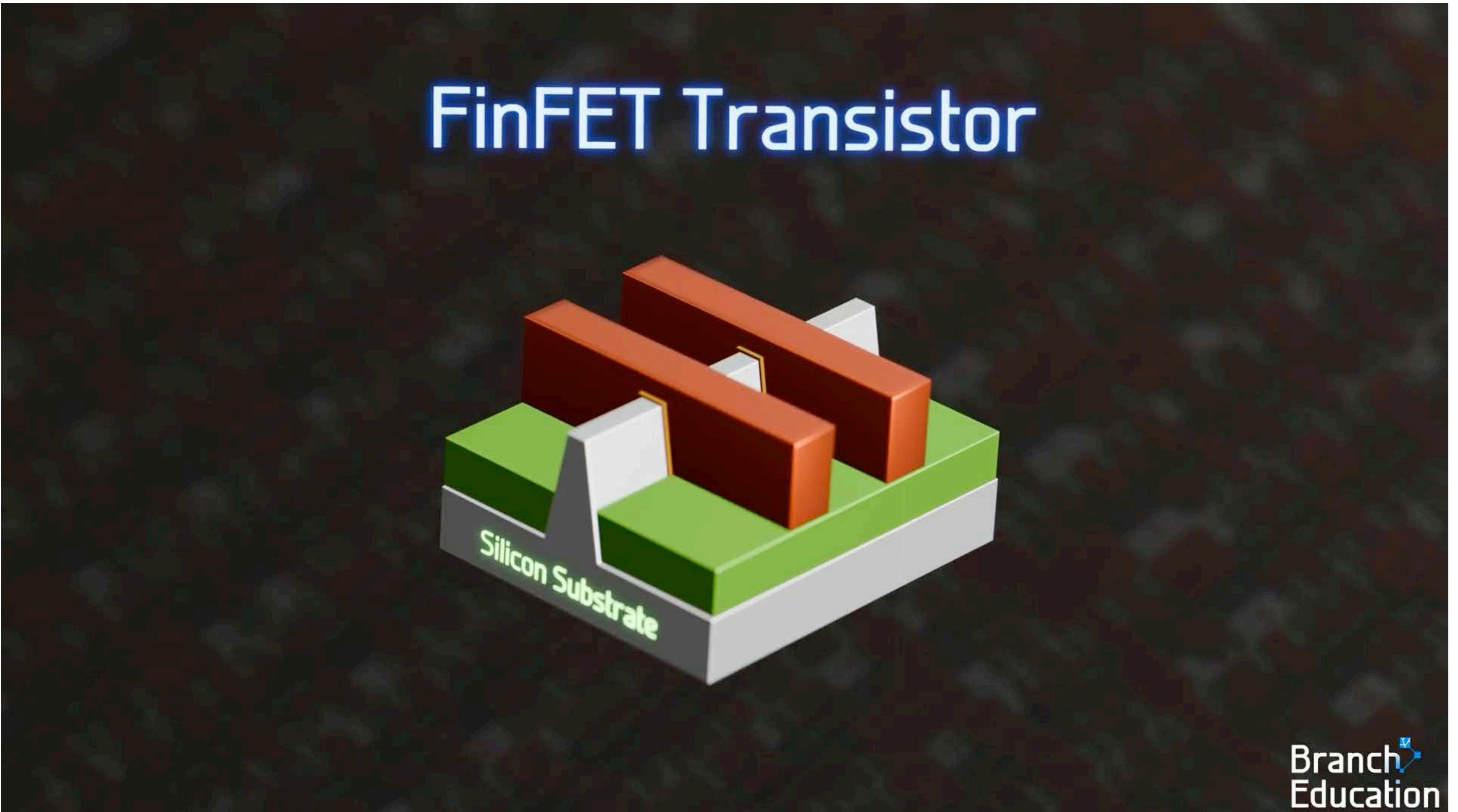

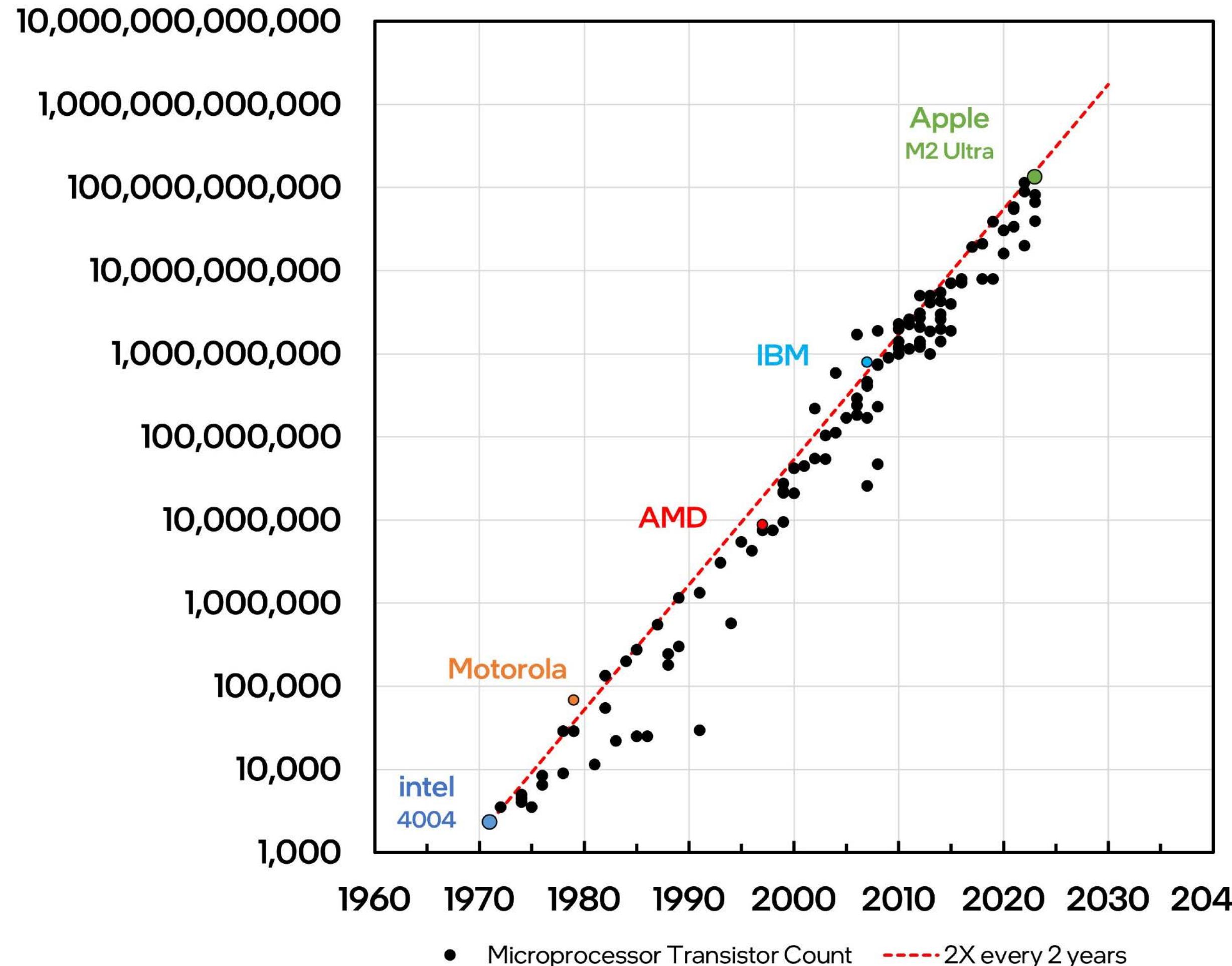

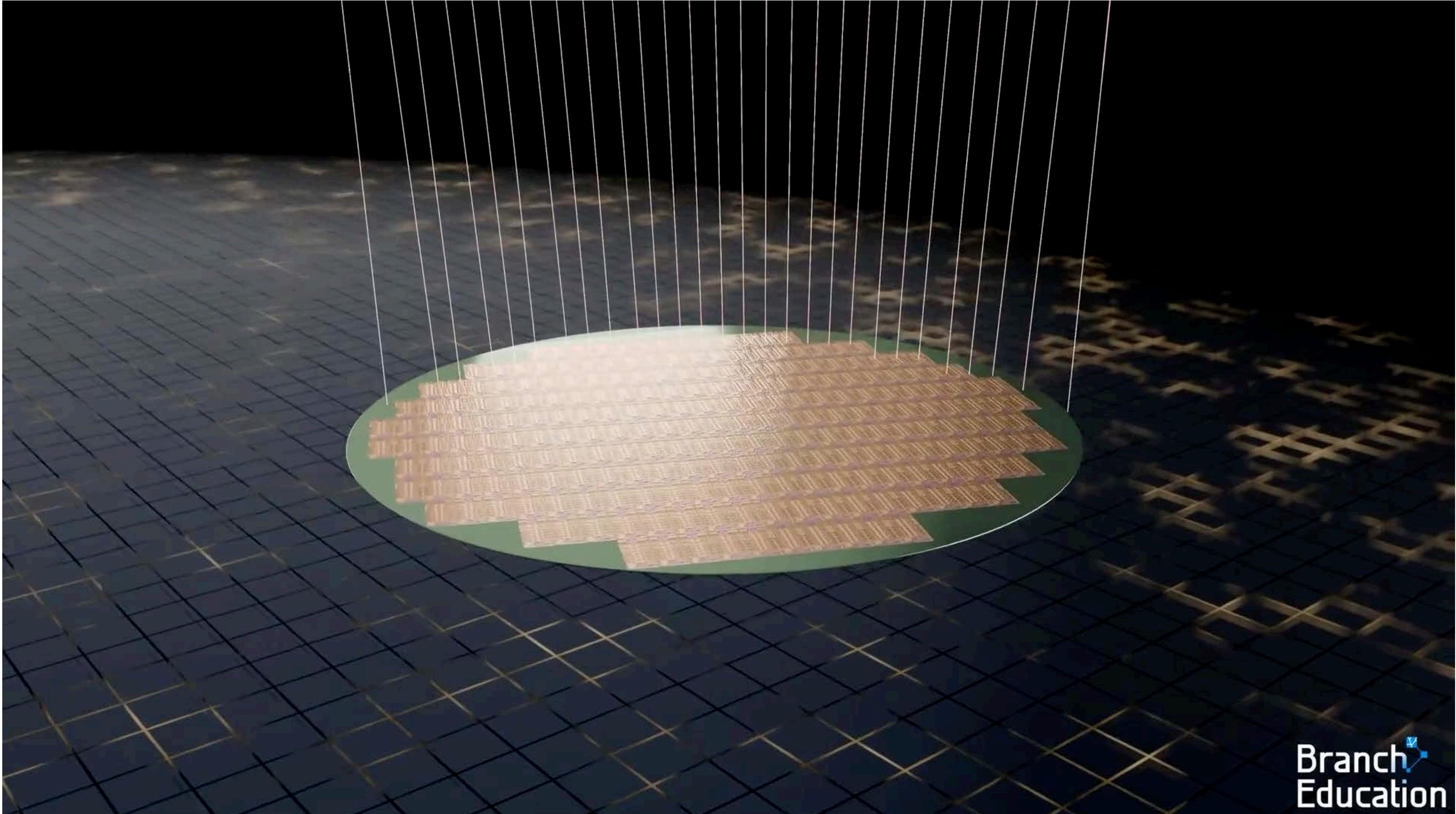

### CPU

- each CPU might have 26 billion transistors

# Layered Manufacturing

Thin Film Processes: MEMS and Microelectronics

12

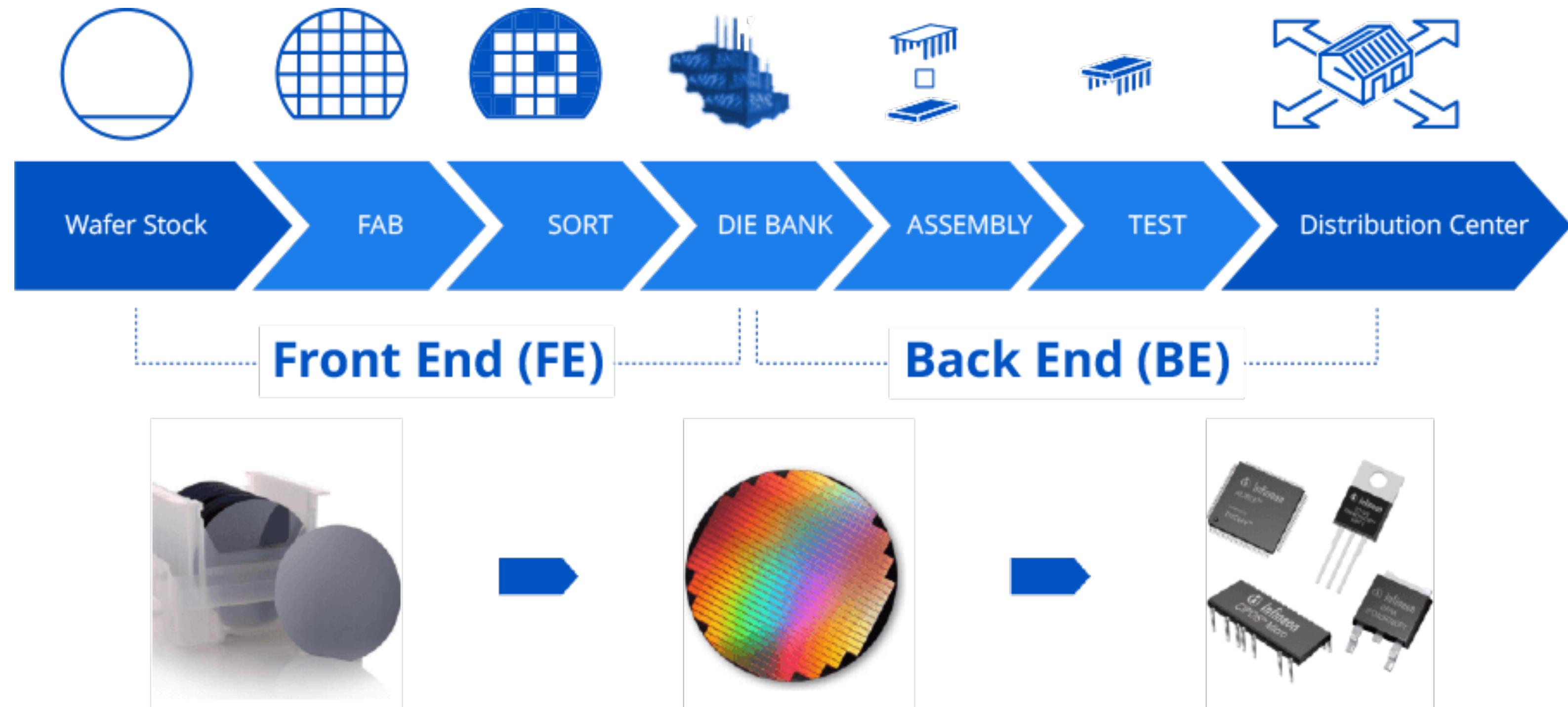

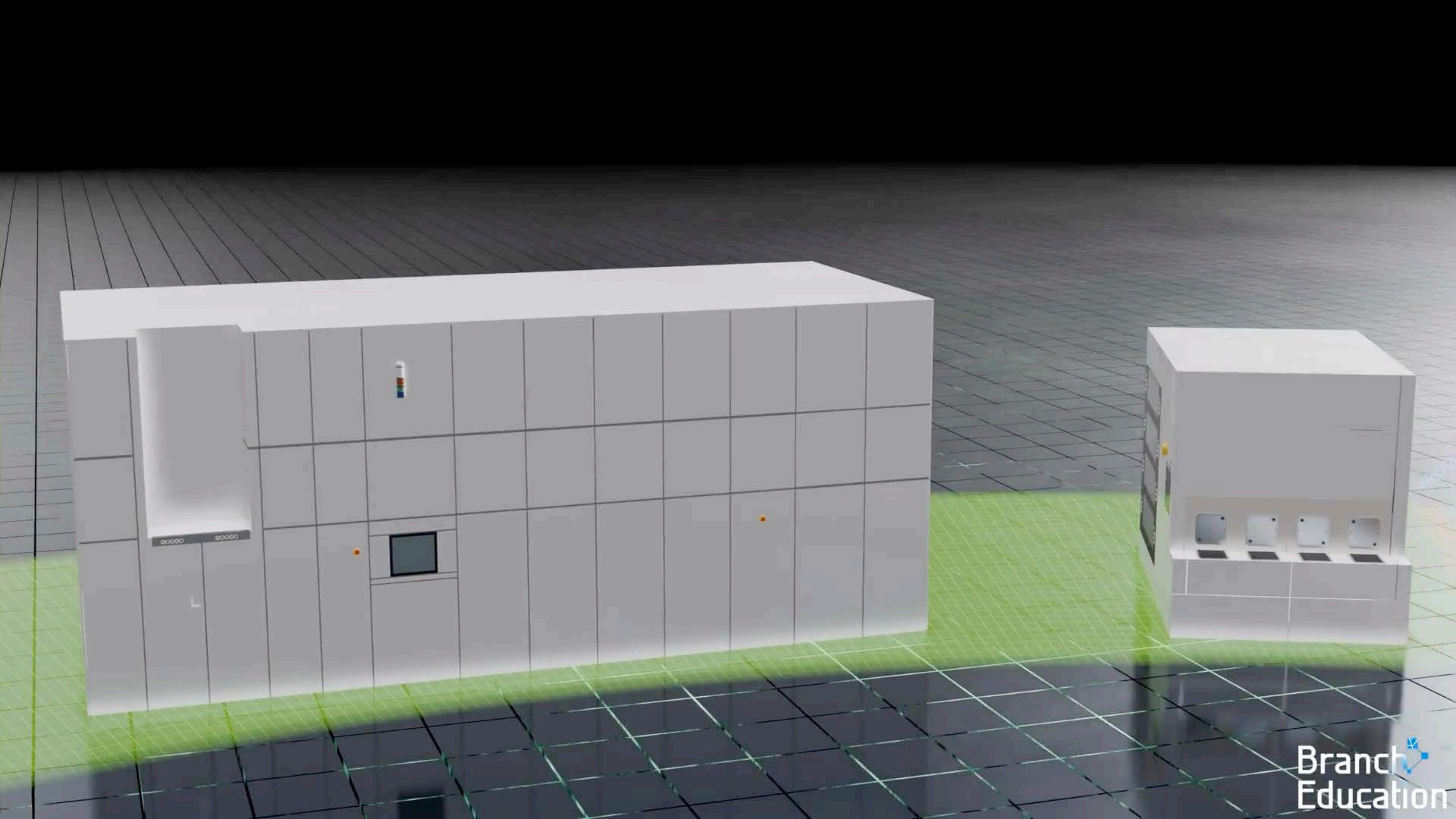

## Semiconductor “Fab” Facility

- \$20 billion → machines ranging from \$3-\$200 million (van-bus size!)

- ~200 major plants globally

- clean room: 8 football fields (minimize static, dust, vibration)

# Layered Manufacturing

Thin Film Processes: MEMS and Microelectronics

13

## Semiconductor “Fab” Facility

FOUP: Front Opening Universal Pod

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

14

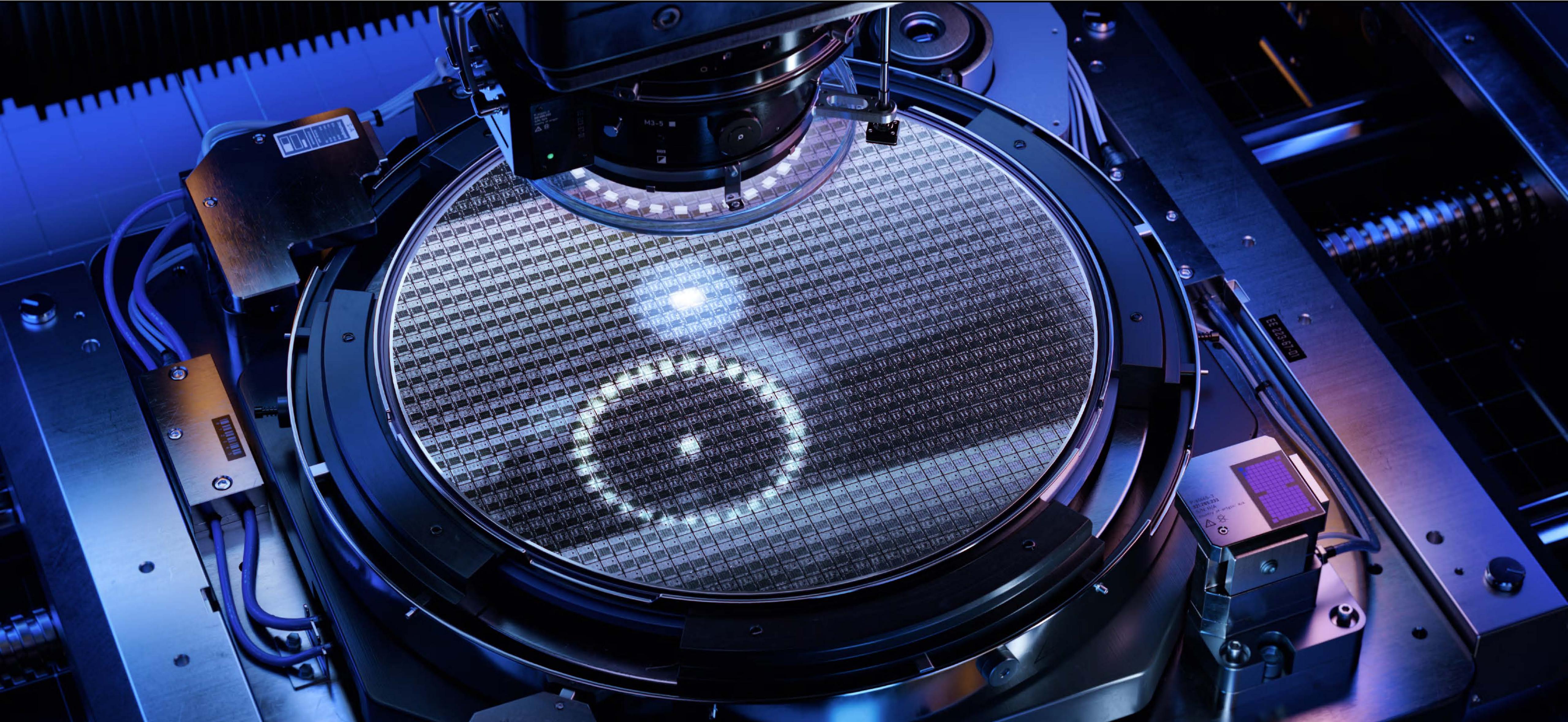

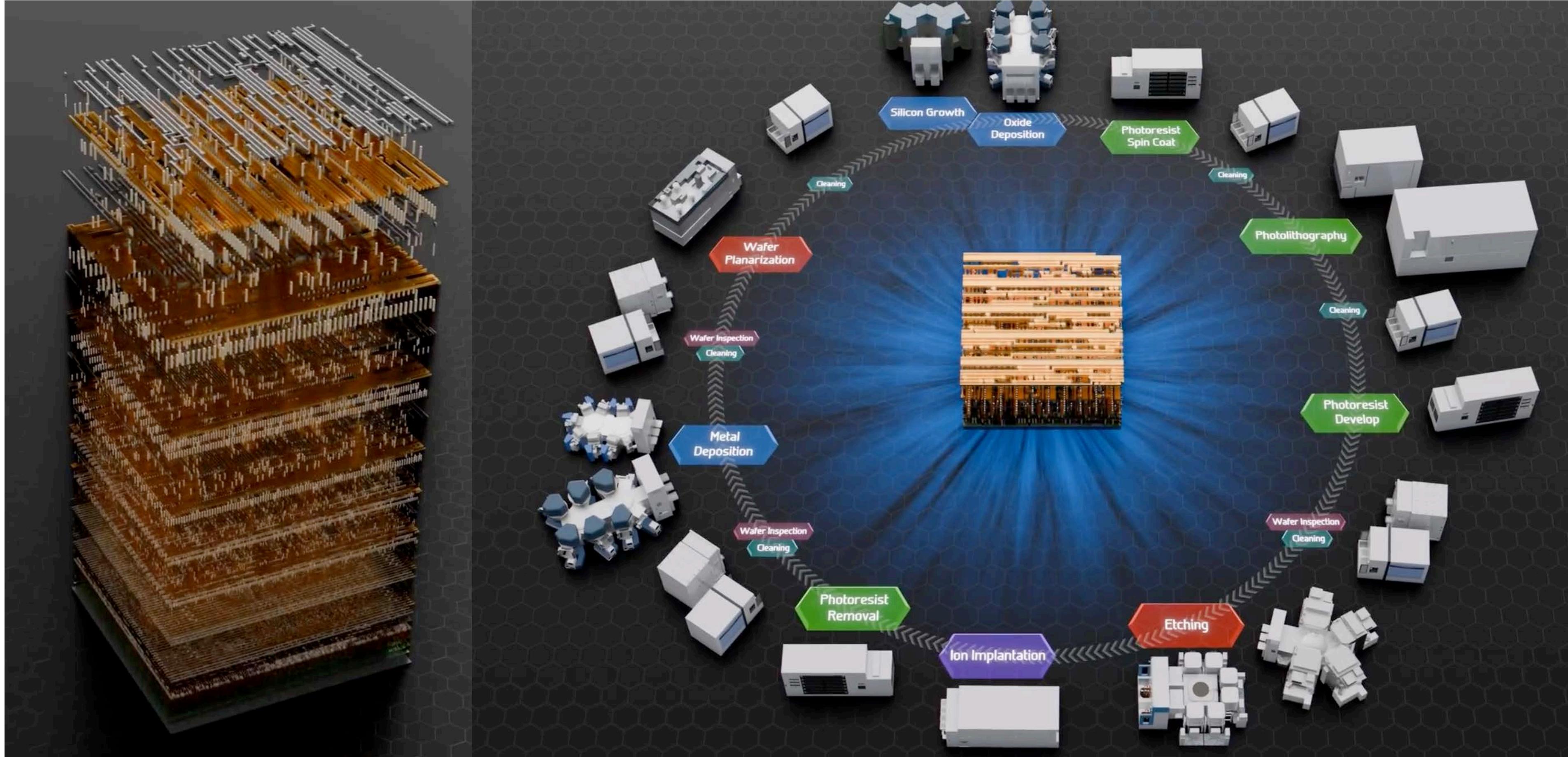

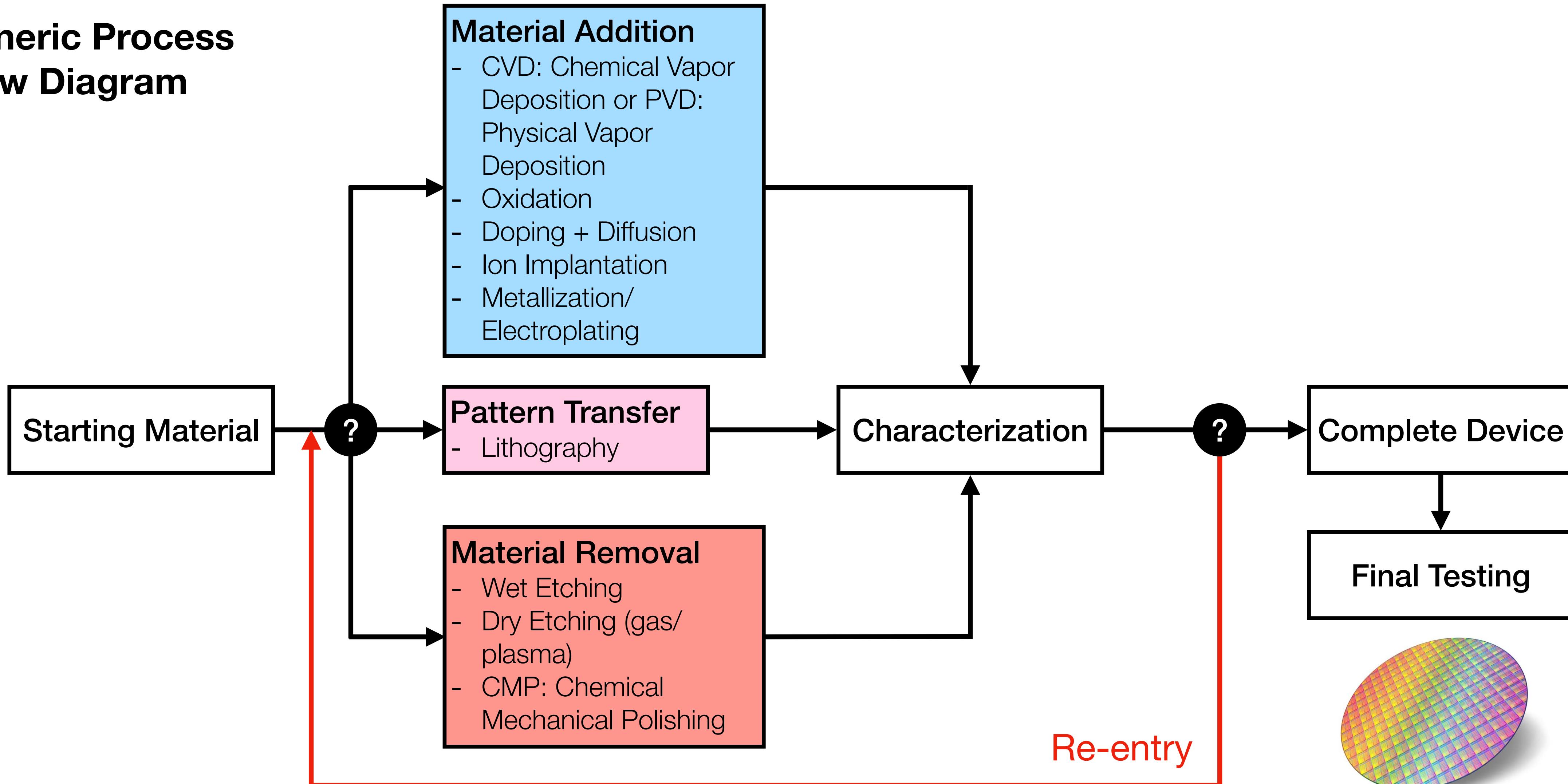

### Generic Process Characteristics

CPU: 80 Layers

takes 3 months to complete 1 wafer → worth more than weight in gold

### Cost

- 1/3 cleaning

- 1/3 photolithography

- 1/3 everything else

SPC: essential!

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

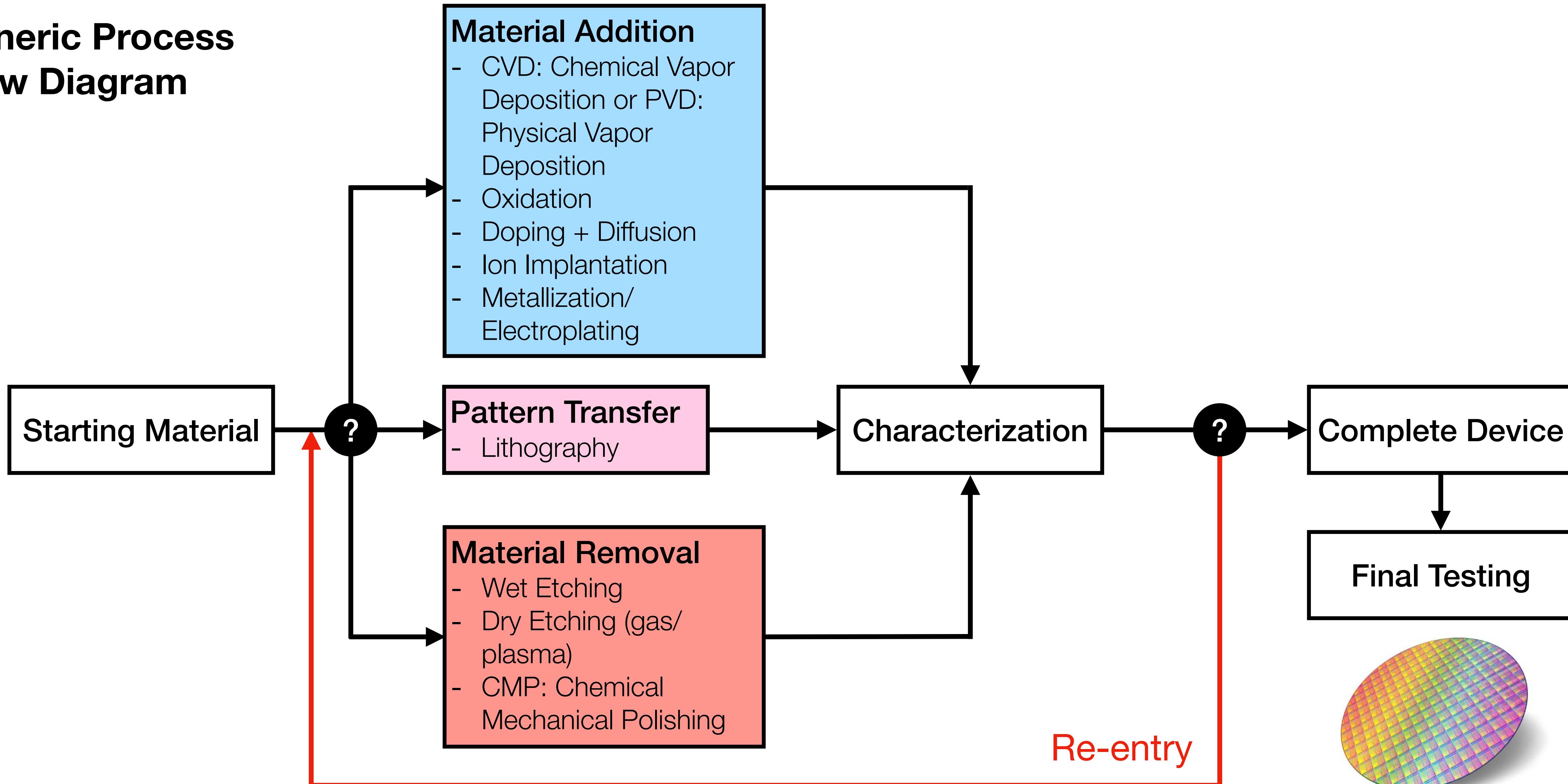

### Generic Process Flow Diagram

# Layered Manufacturing

Thin Film Processes: MEMS and Microelectronics

16

## Process Preview

# How Chips Are Manufactured

with Optics from ZEISS

ZEISS Semiconductor Manufacturing Technology

[www.zeiss.com/smt](http://www.zeiss.com/smt)

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

18

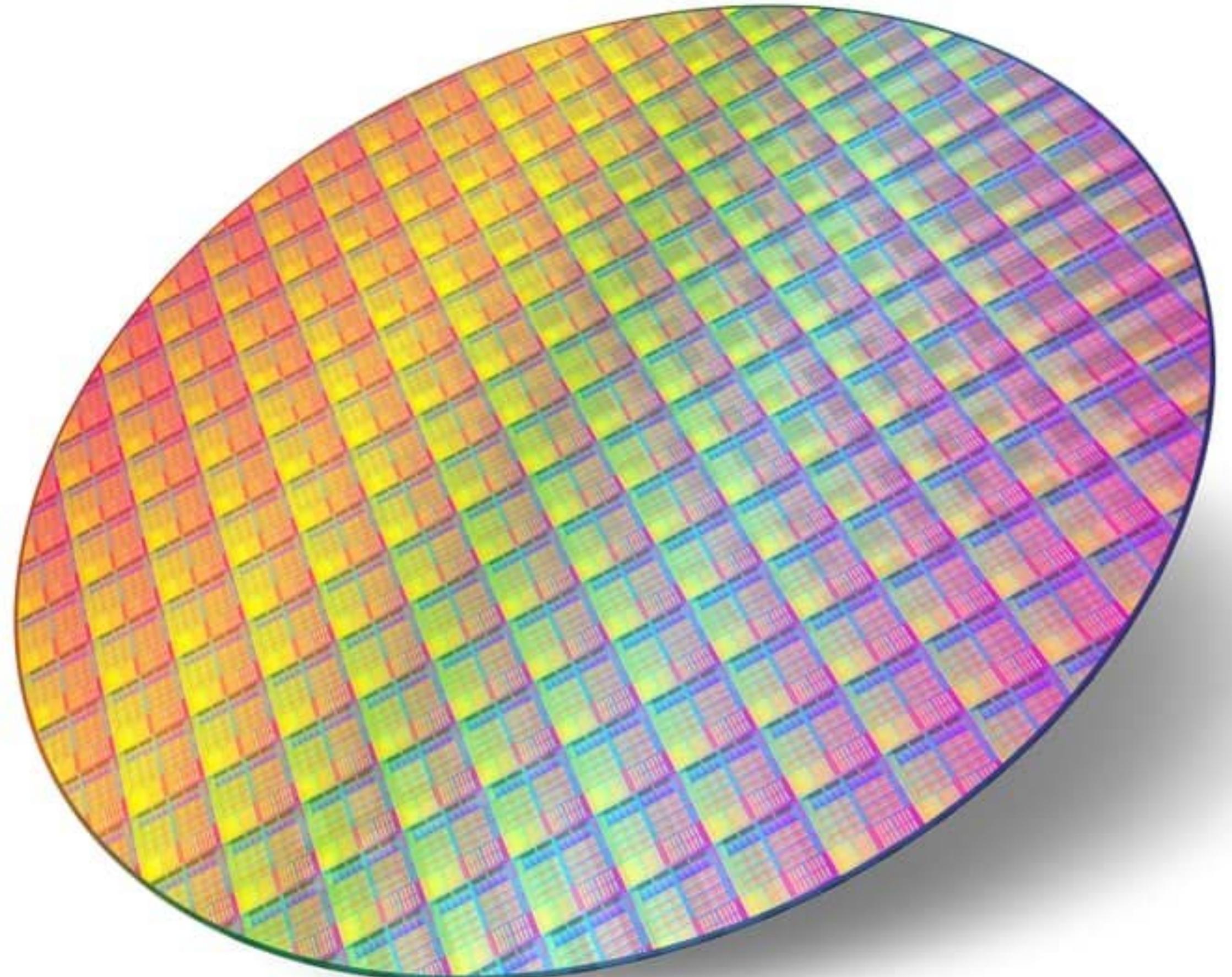

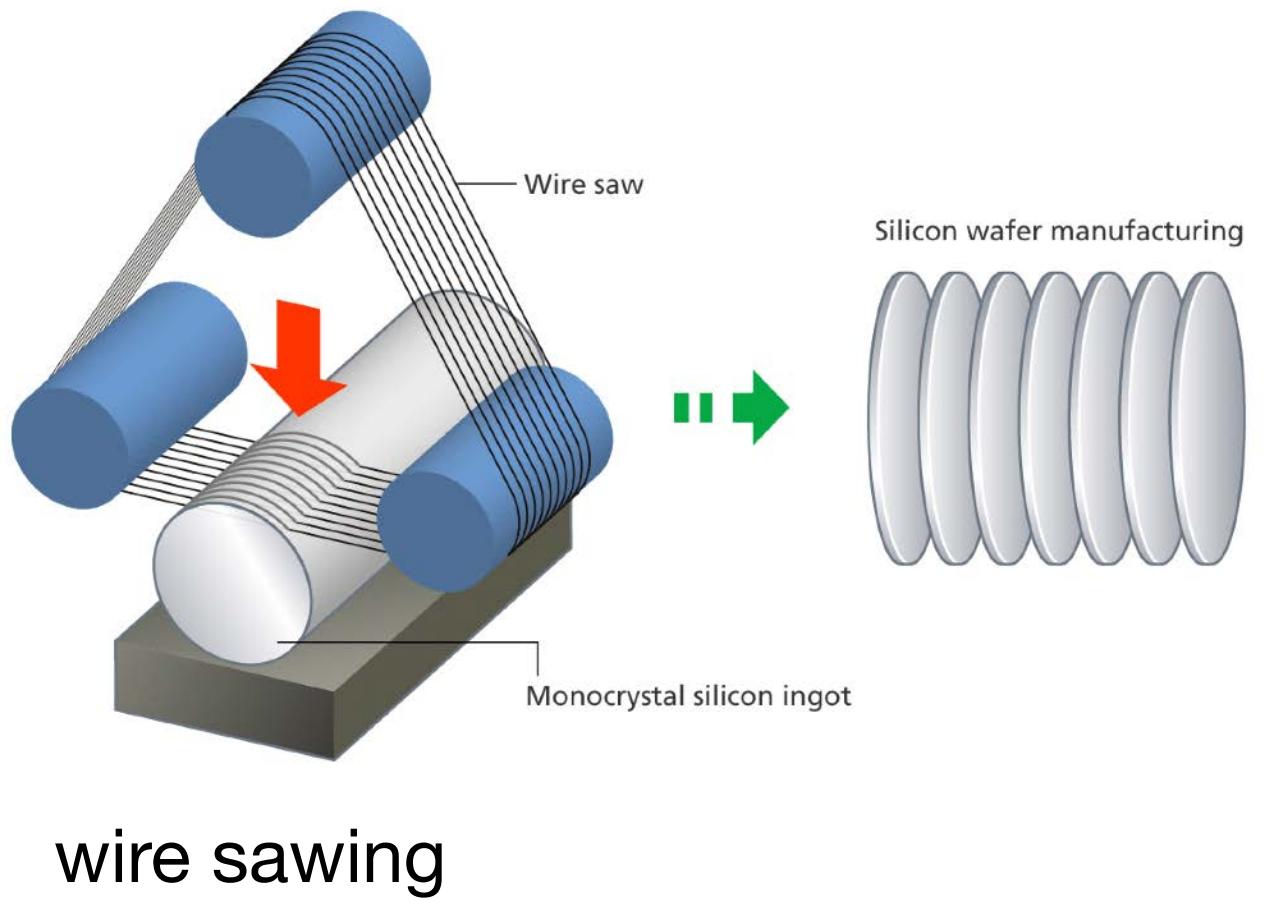

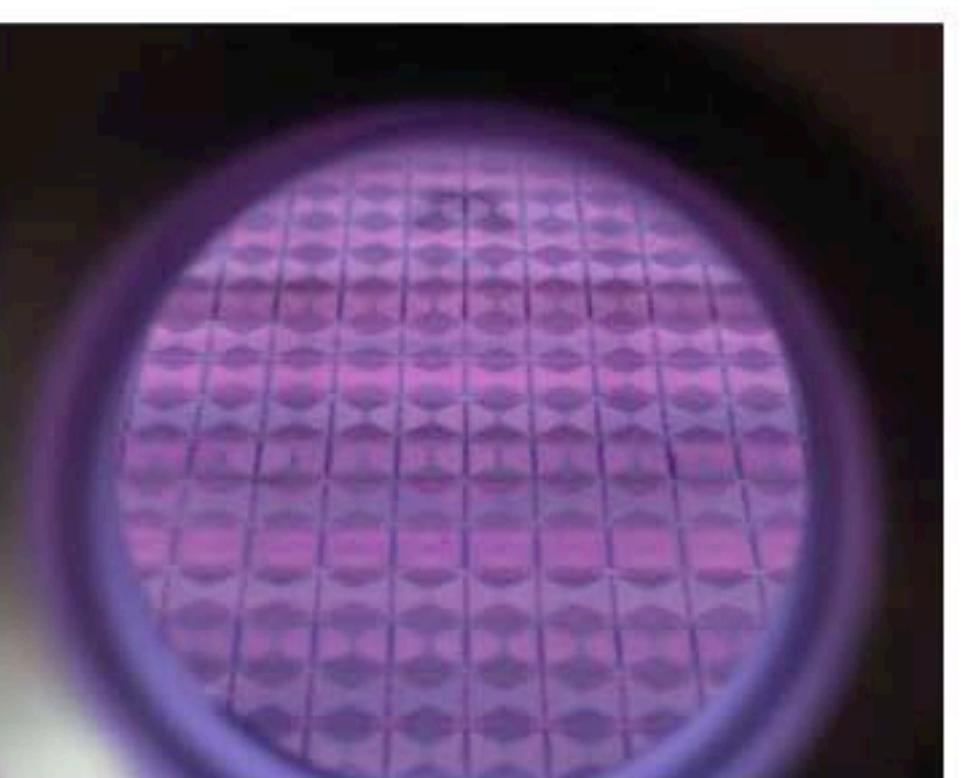

### Process Flow Example: Starting Wafer

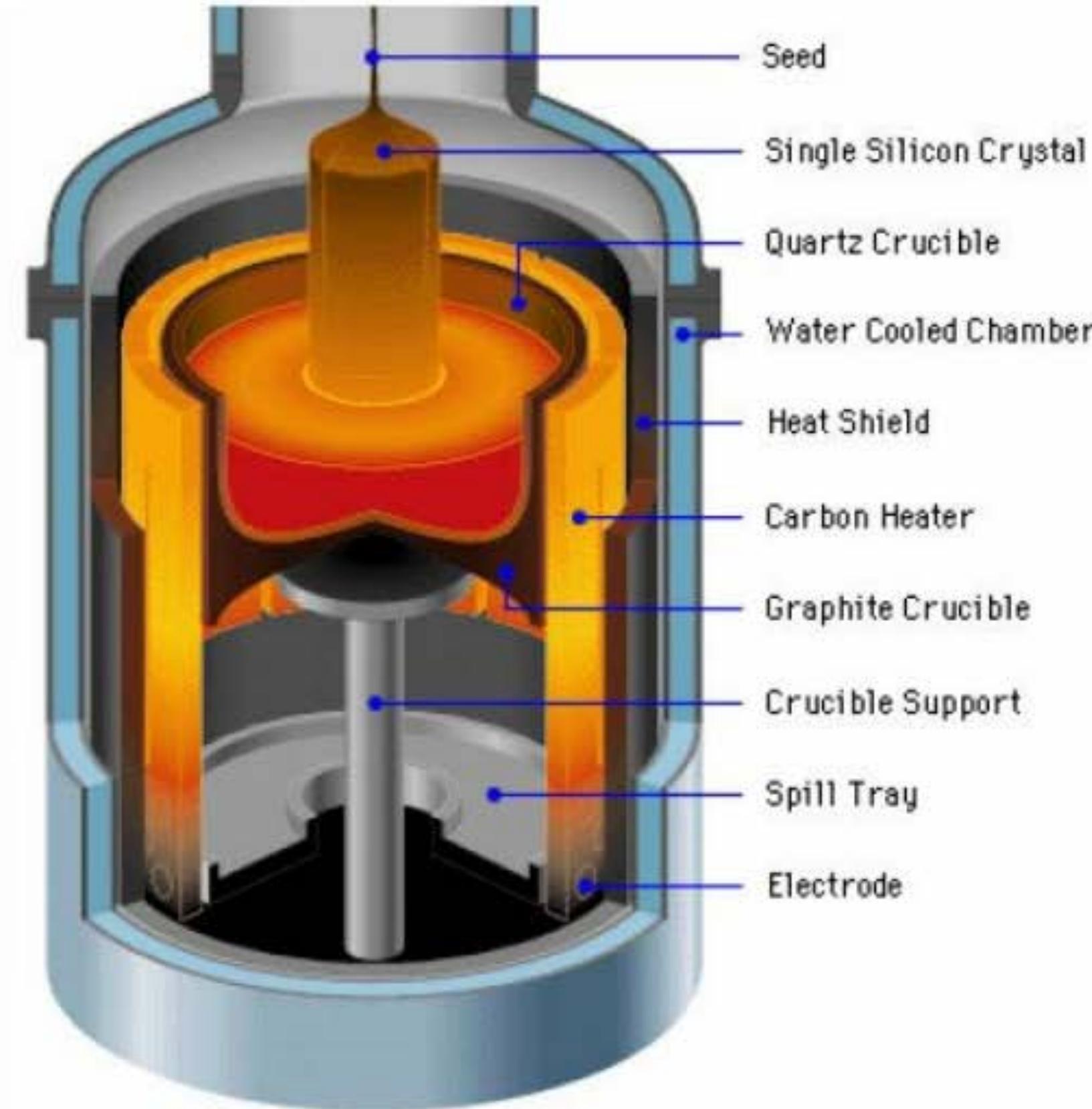

Why Silicon? Need a good **semiconductor**, good fit for manufacturing

alternative: gallium arsenide - better but harder to grow

can alter silicon's lattice structure

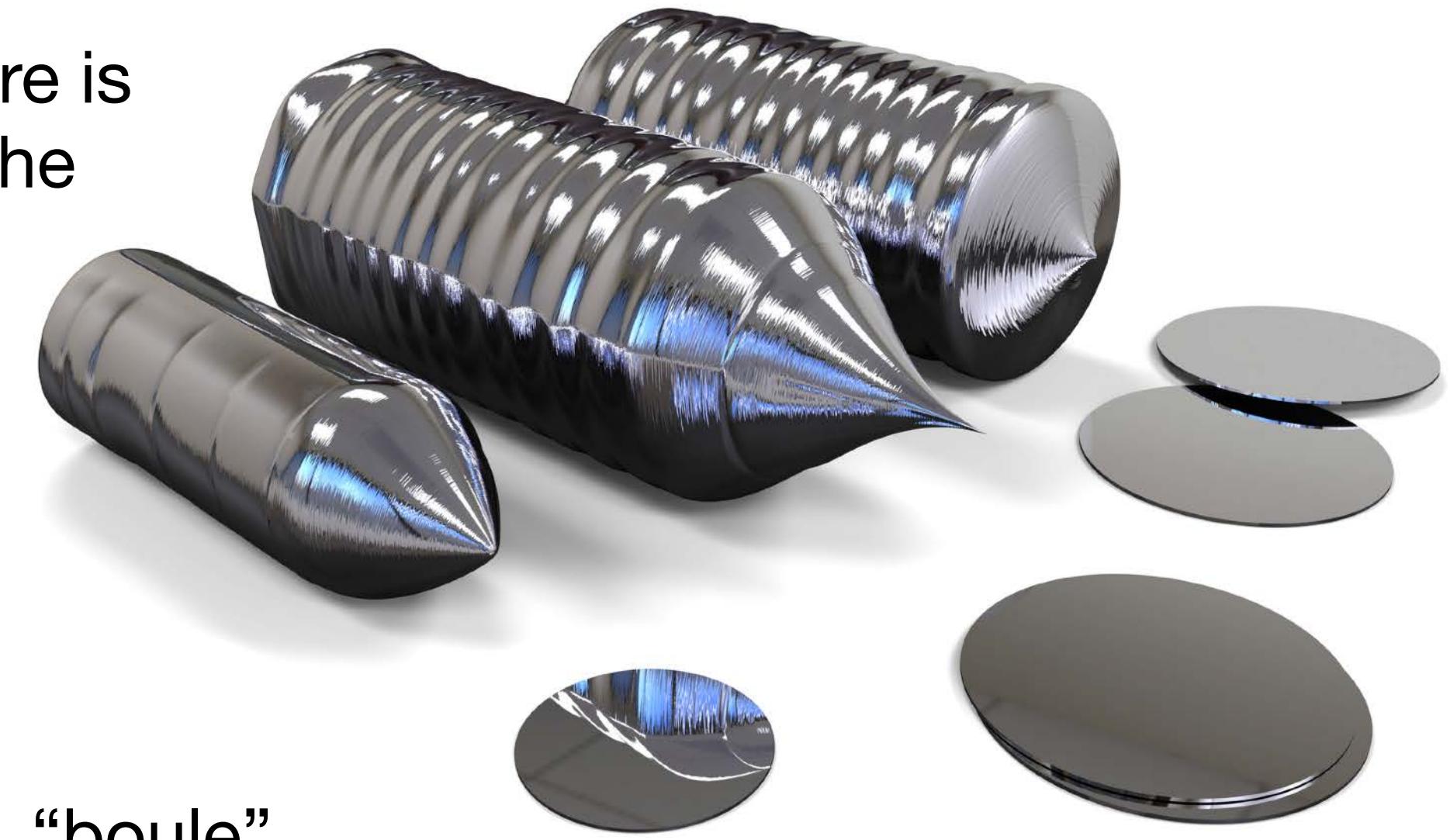

Why circular? rotating is part of the mono-crystalline growth process

means there is waste on the edges...

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

19

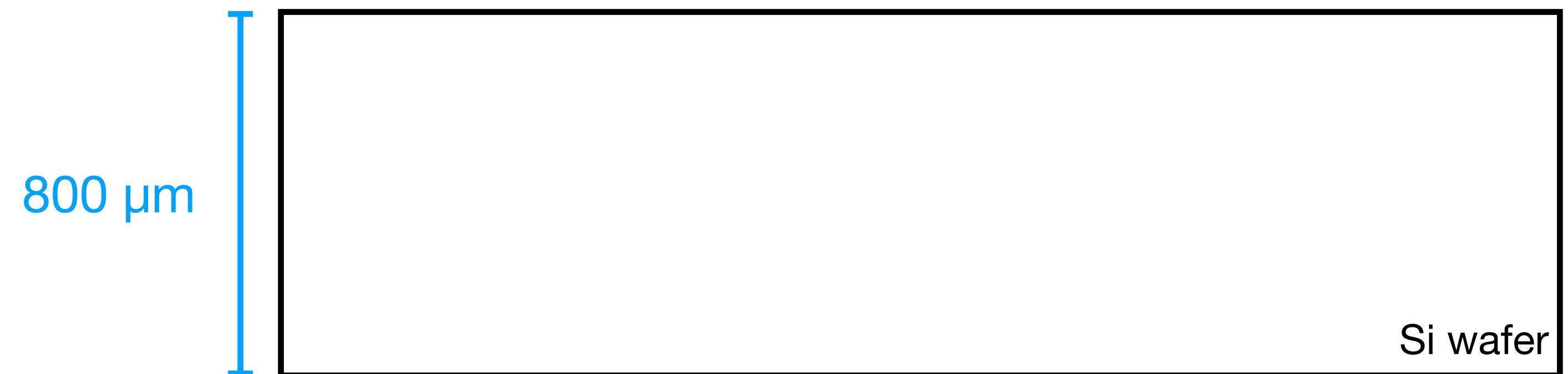

### Process Flow Example: Starting Wafer

#### Starting Wafer

- characterize: electrical measurement

#### Clean Wafer

- critical resource: water and chemicals for cleaning

Wafer Diameter: 300mm (~12in)

4" → 8" → **12"** (→ 18"?)

wire sawing

ID sawing

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

20

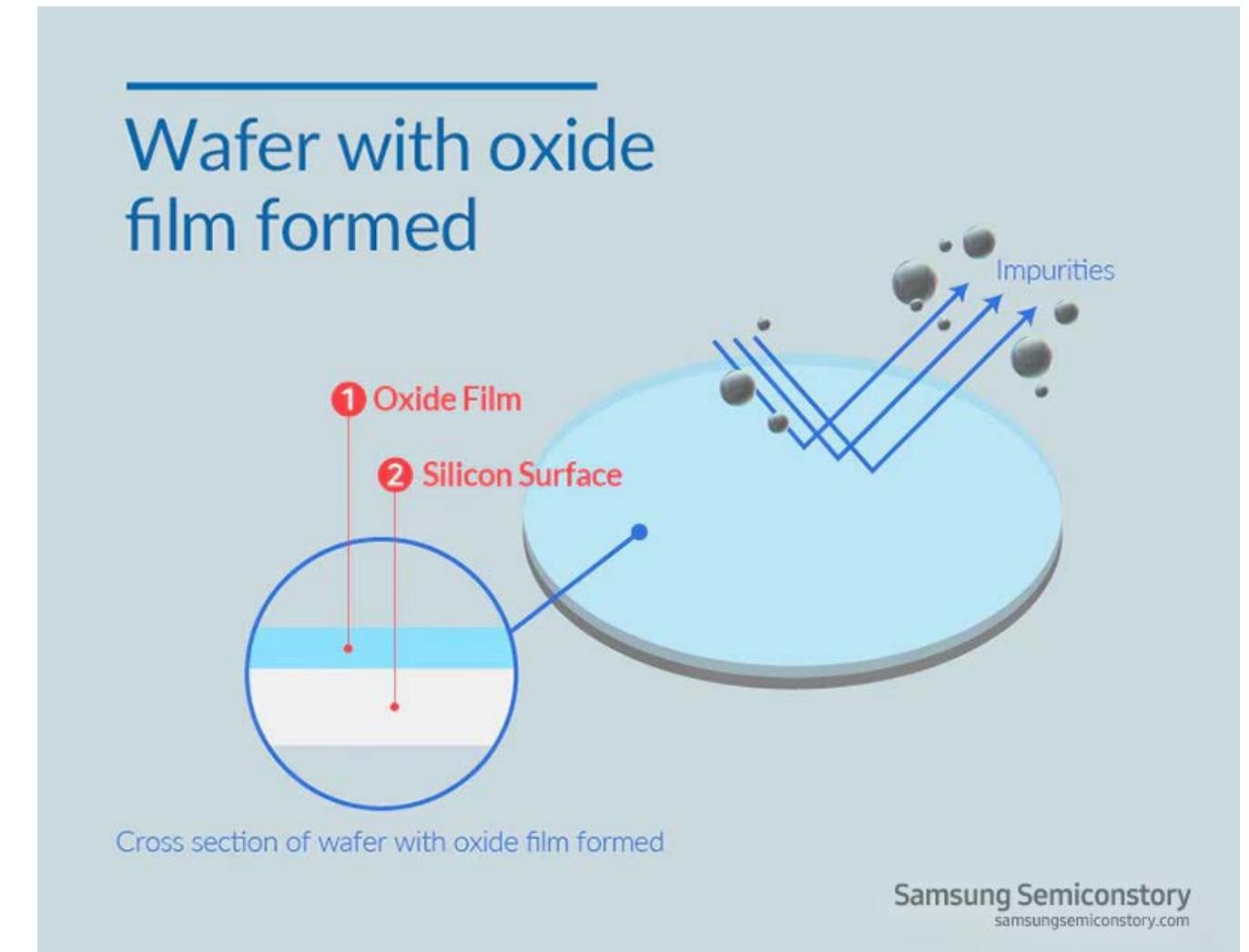

### Process Flow Example: Field Oxidation

#### Field Oxidation

- protect wafer

- furnace: oxygen/water vapor + temperature increase

- some silicon is consumed during this process

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

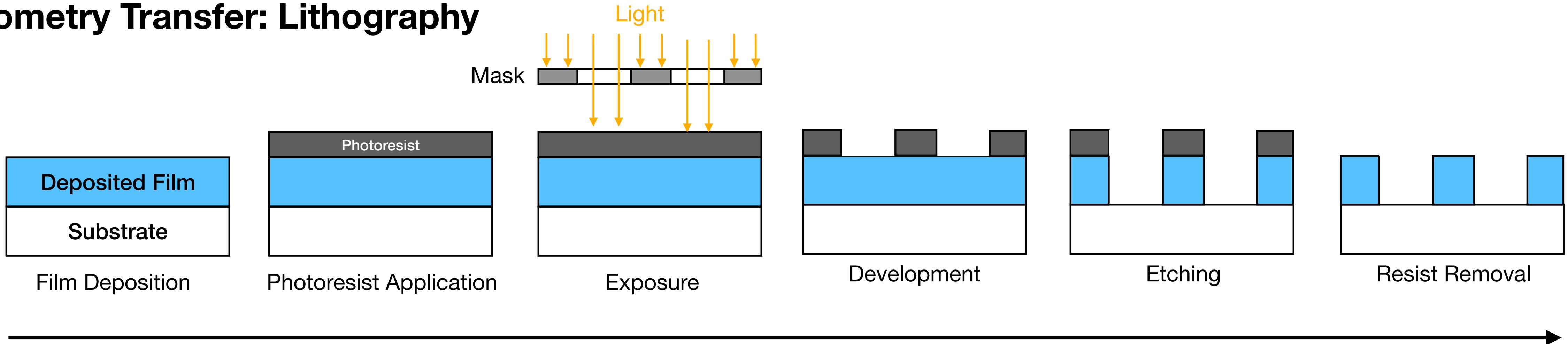

### Process Flow Example: Pattern Field Oxide

Pattern the field oxide

- apply photoresist, expose and develop

- etch field oxide

- remove photoresist

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

22

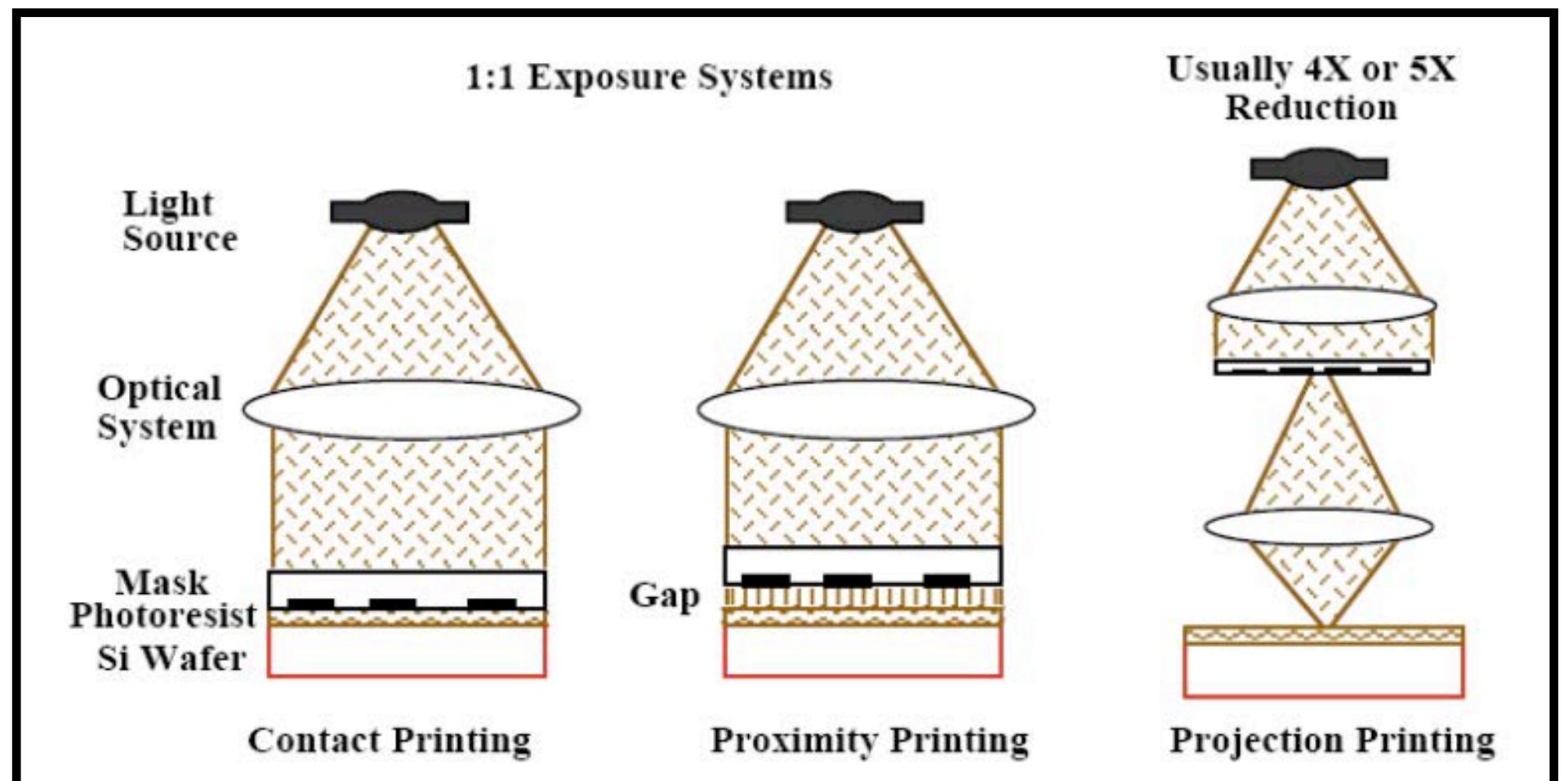

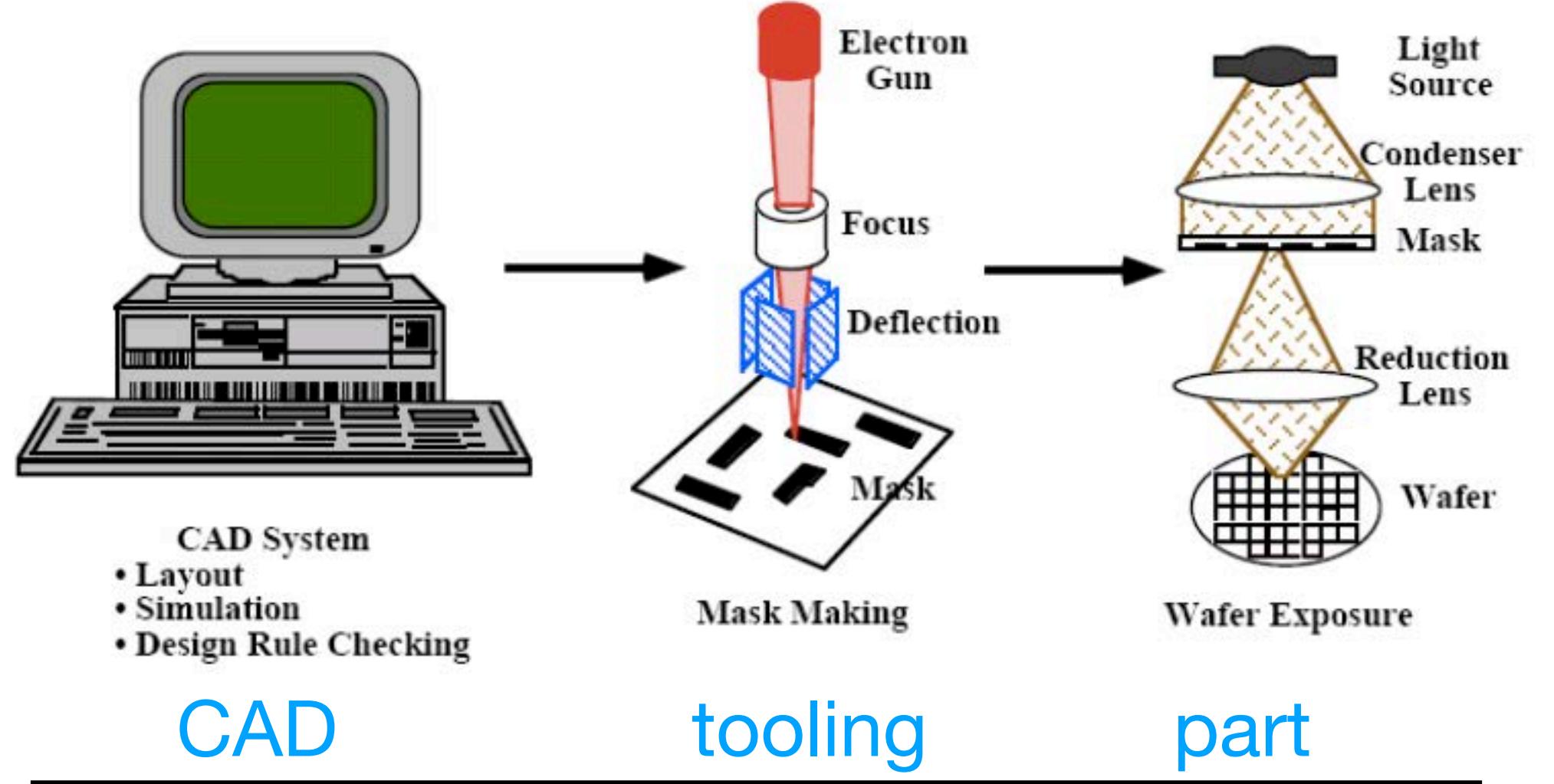

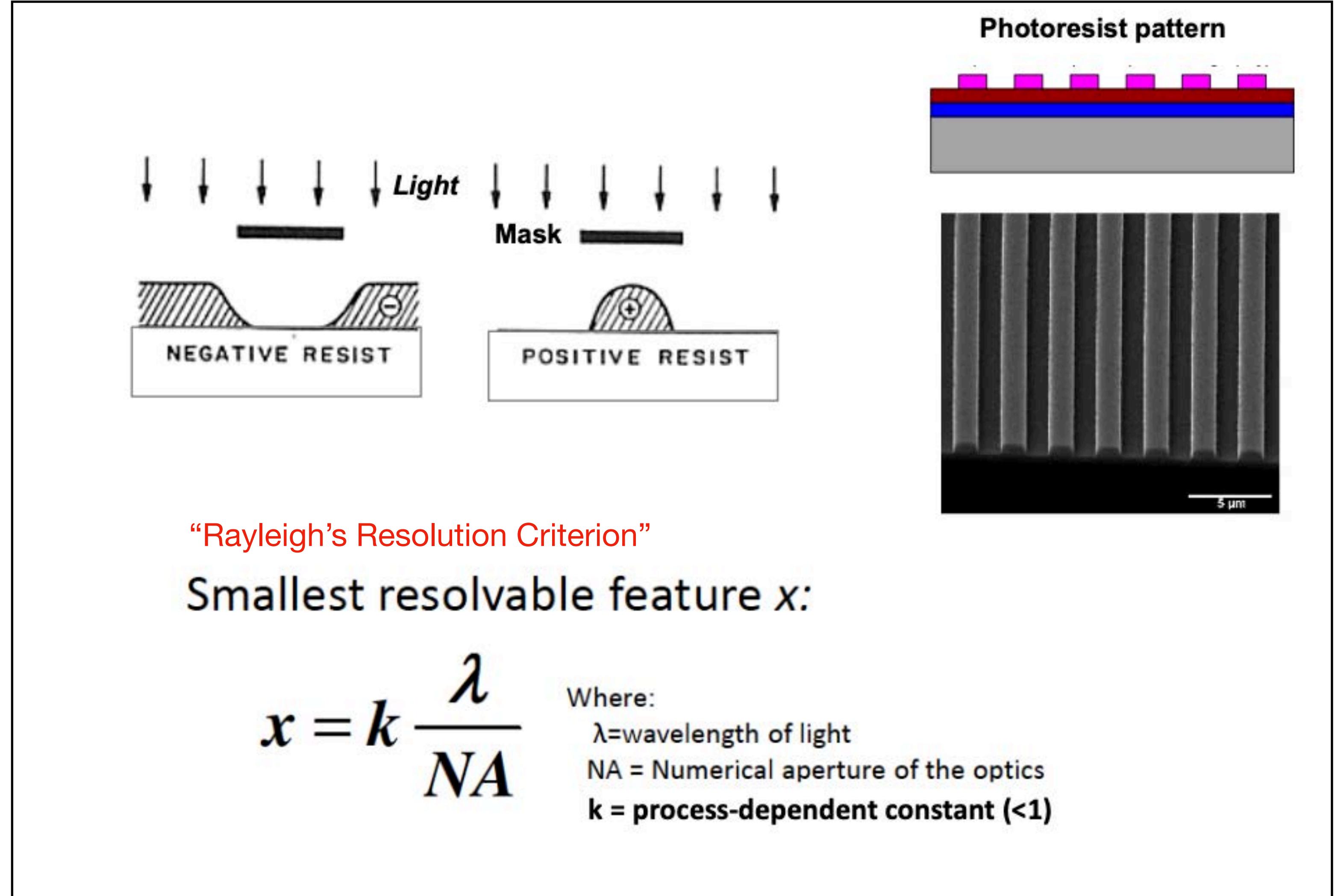

### Geometry Transfer: Lithography

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

23

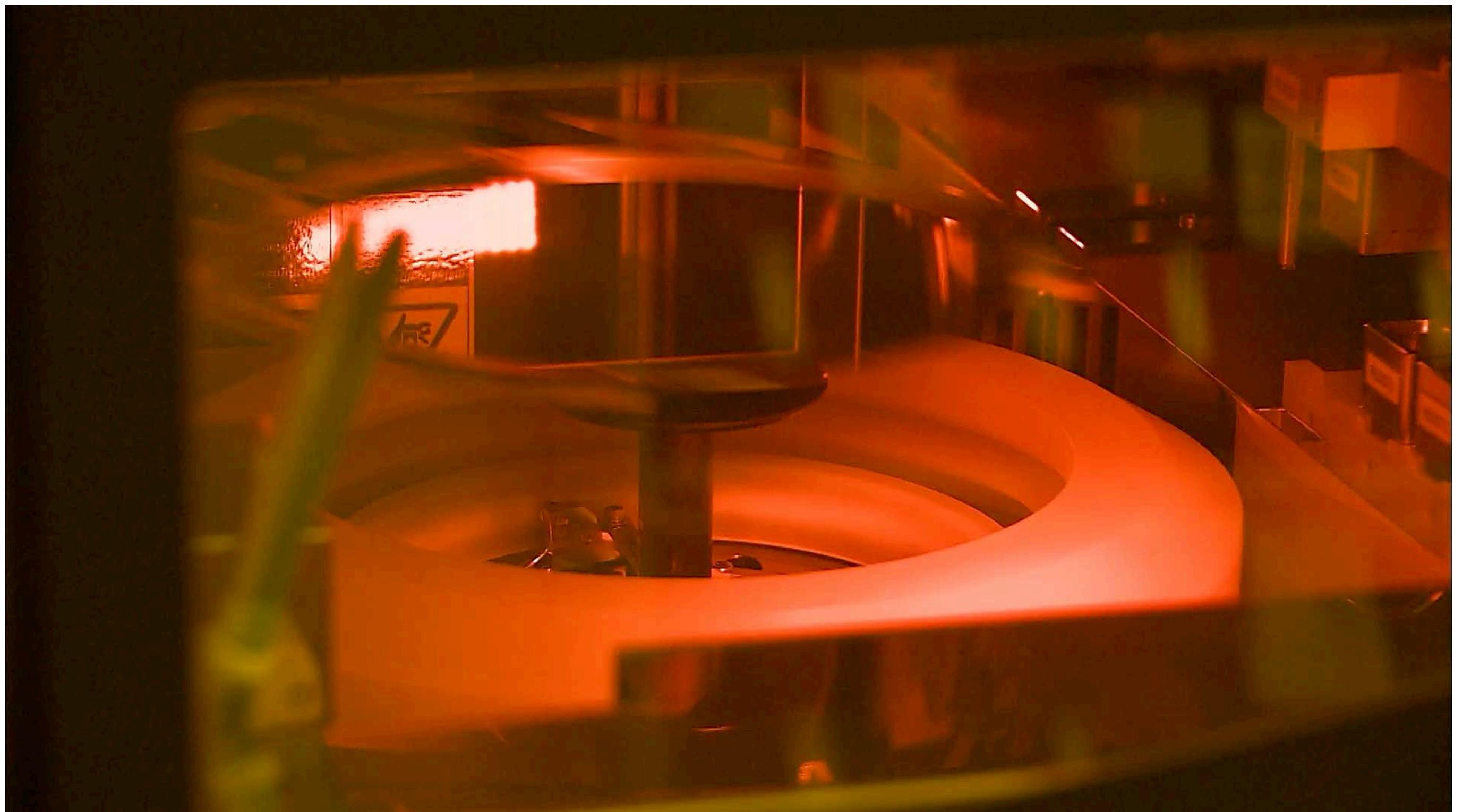

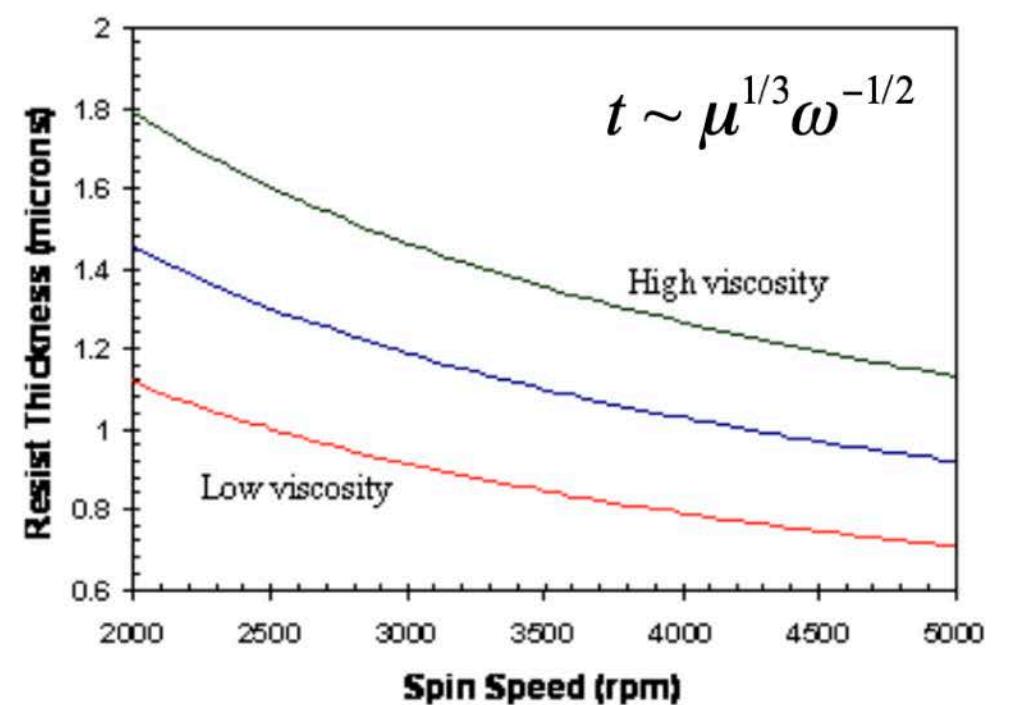

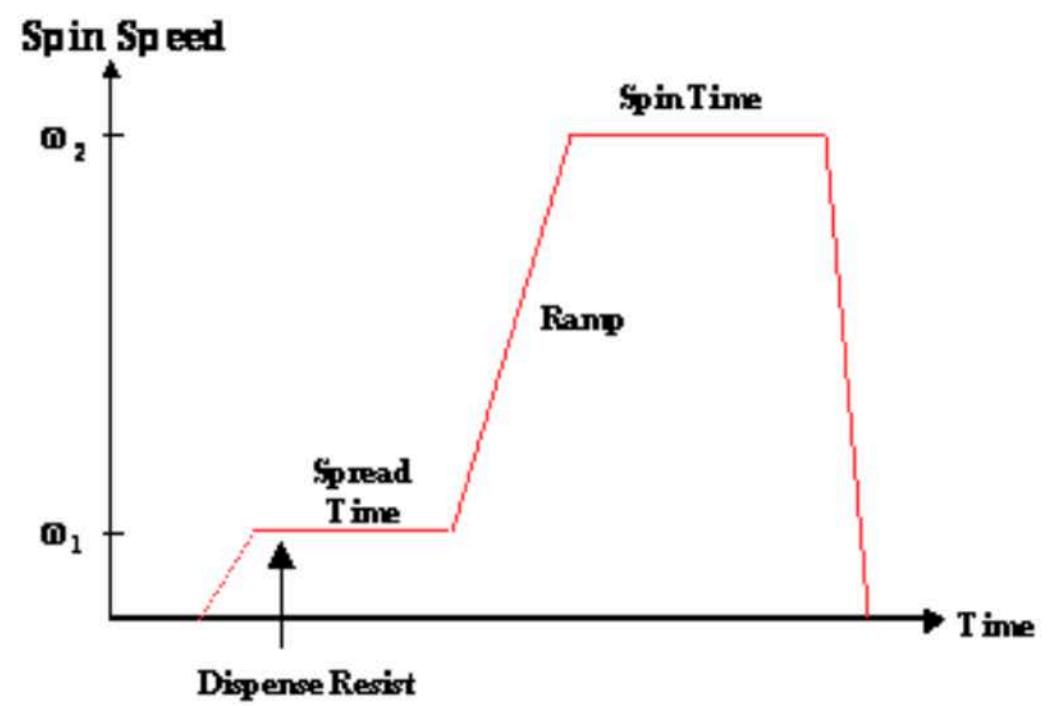

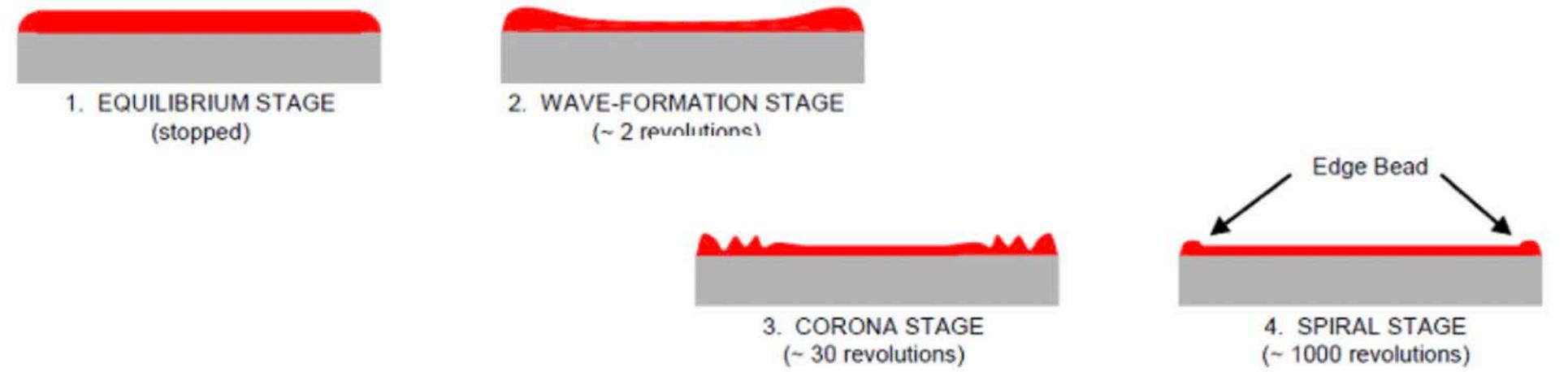

### Lithography: Photoresist Application

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

24

### Lithography: Patterning

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

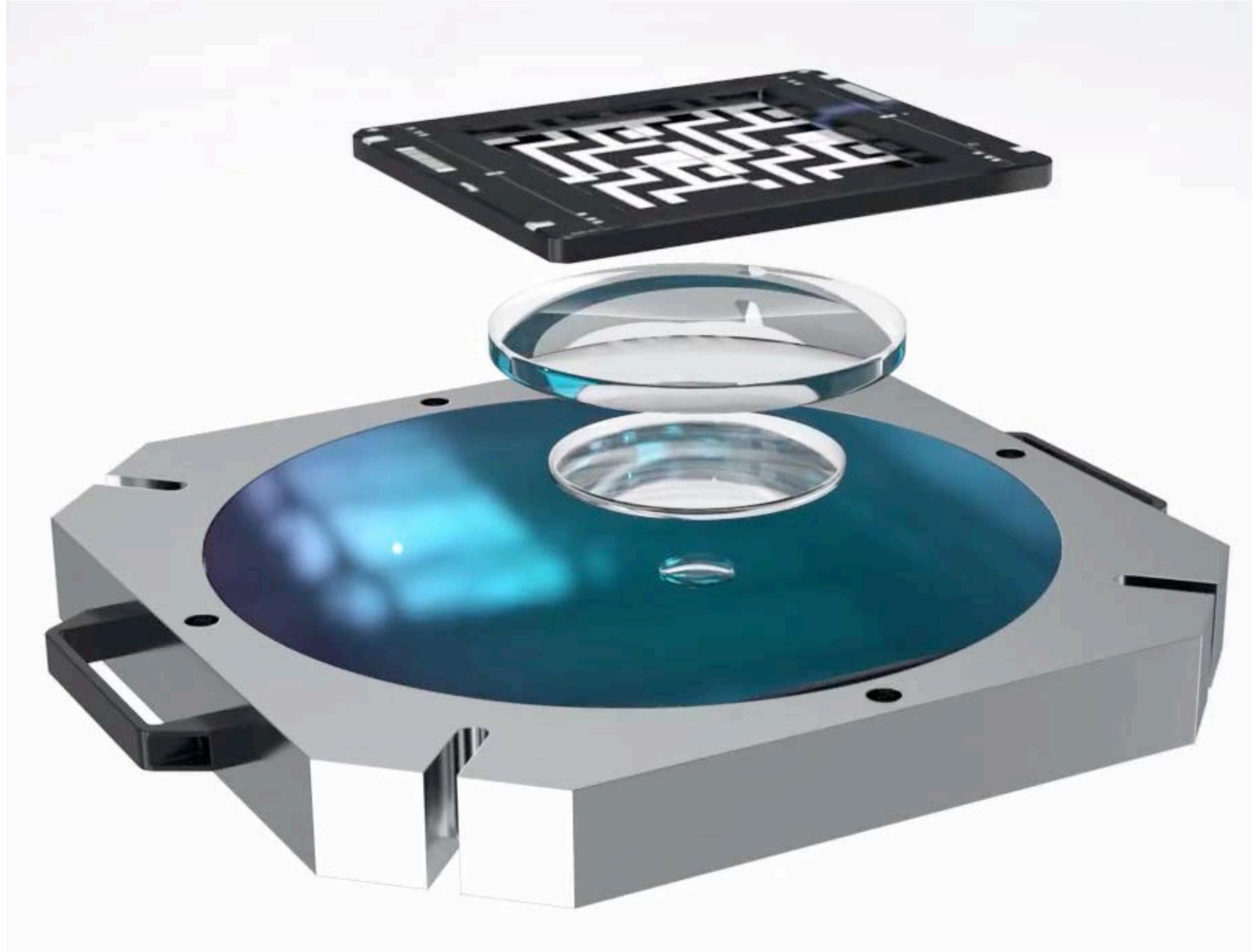

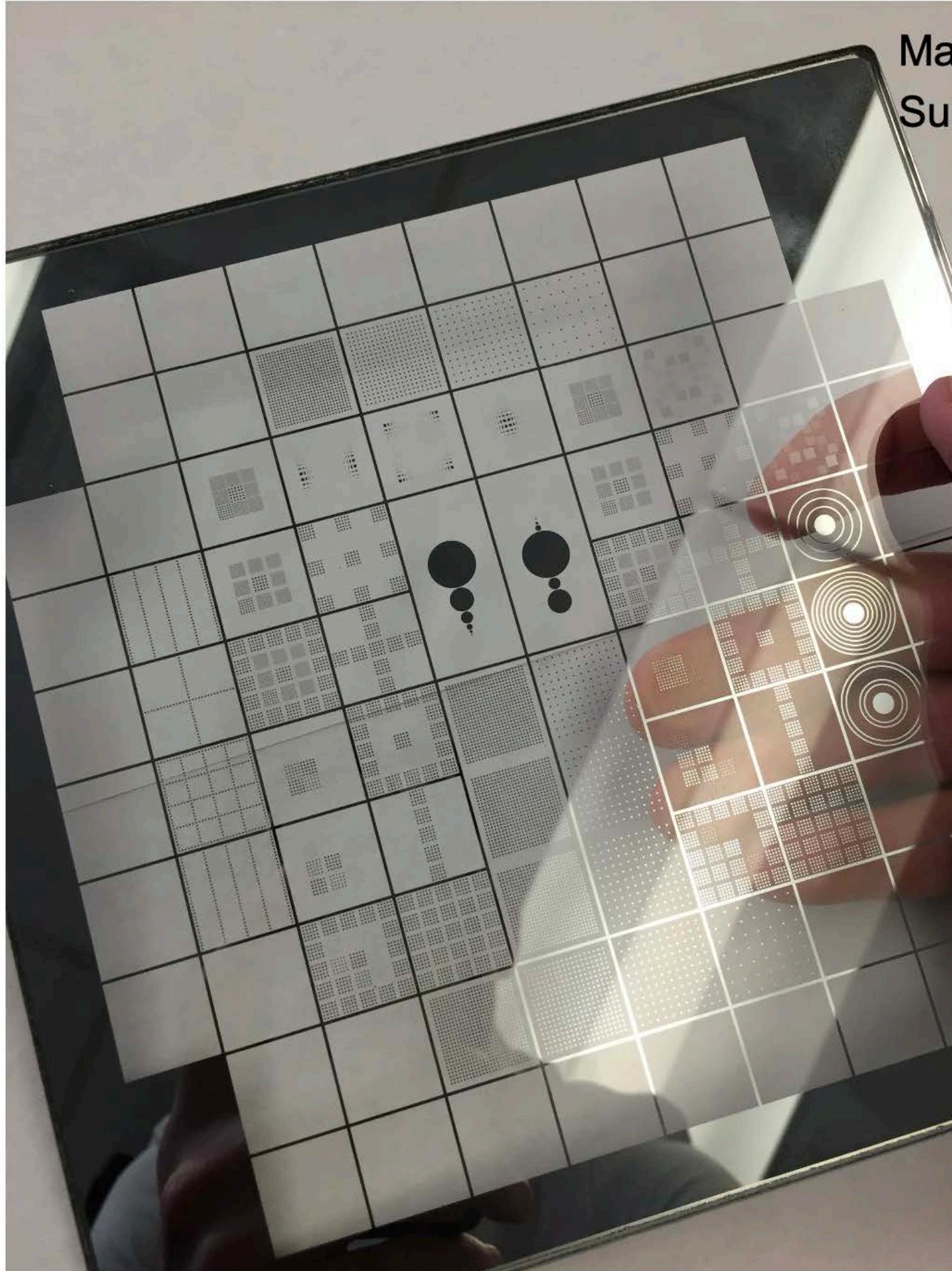

### Lithography and Patterning: Photo Masks

Could be using 80 masks for 80 layers

Mask patterns = Chrome

Substrate = Glass (soda-lime or quartz)

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

### Lithography and Patterning

EUV Light: Extreme Ultra Violet

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

### Lithography and Patterning: Light Generation

**13.5**

**NANOMETERS**

...is the wavelength of the extreme ultraviolet (EUV) light that is created, which facilitates the manufacture of structural sizes of less than 10 nanometers.

**50,000**

**TIN DROPLETS PER SECOND**

... are hit by the TRUMPF Laser Amplifier, to create EUV rays for substrate exposure.

**100,000,000**

**TRANSISTORS PER SQUARE MILLIMETER**

... and more can be placed on a single microchip due to EUV lithography - which is almost inconceivable.

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

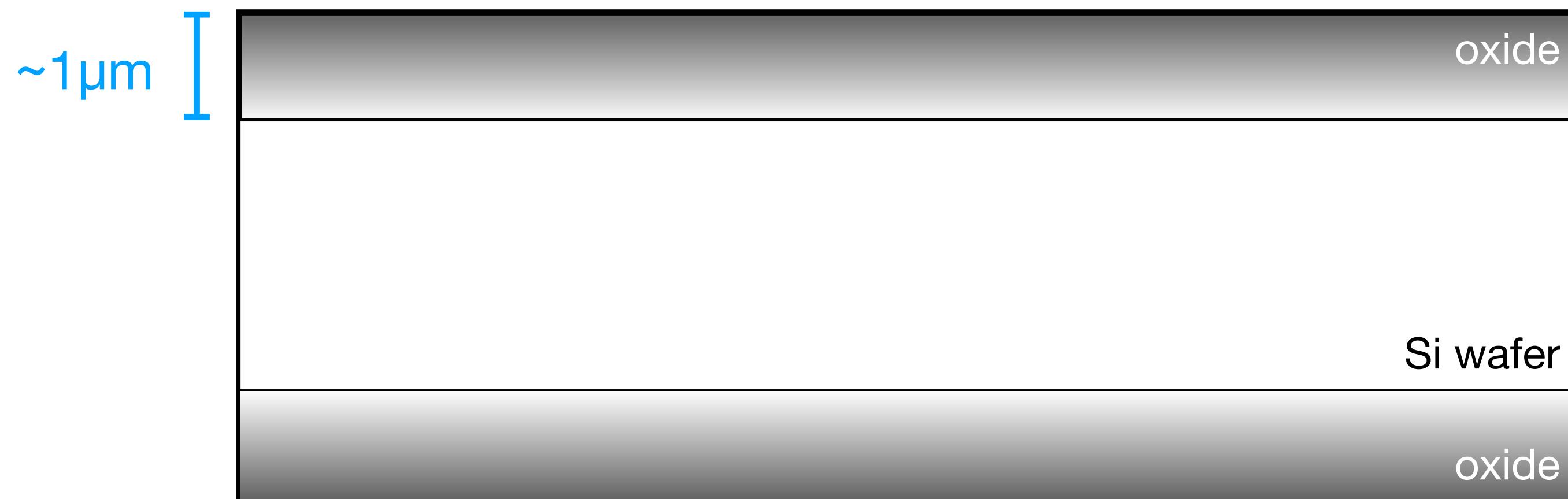

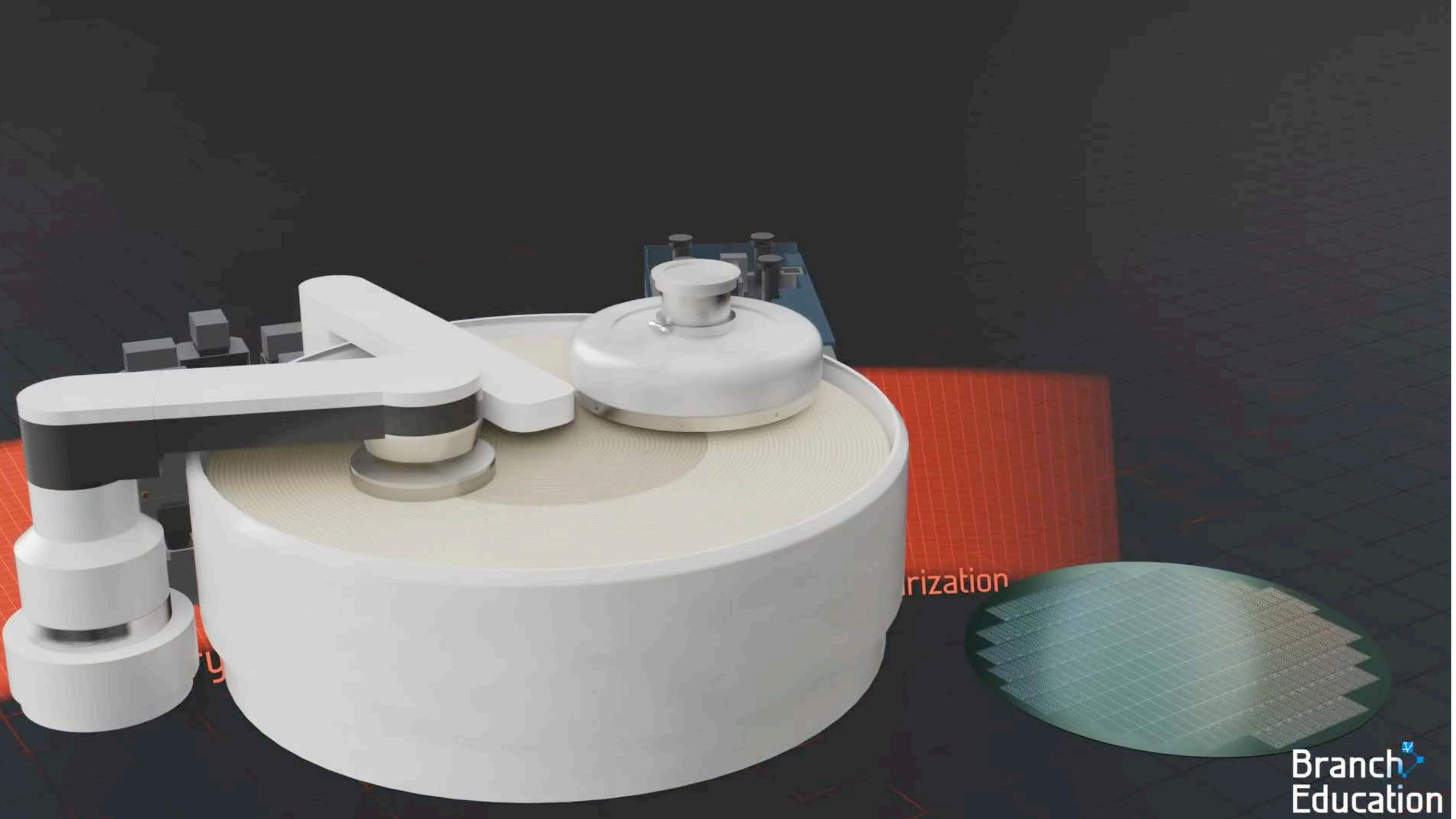

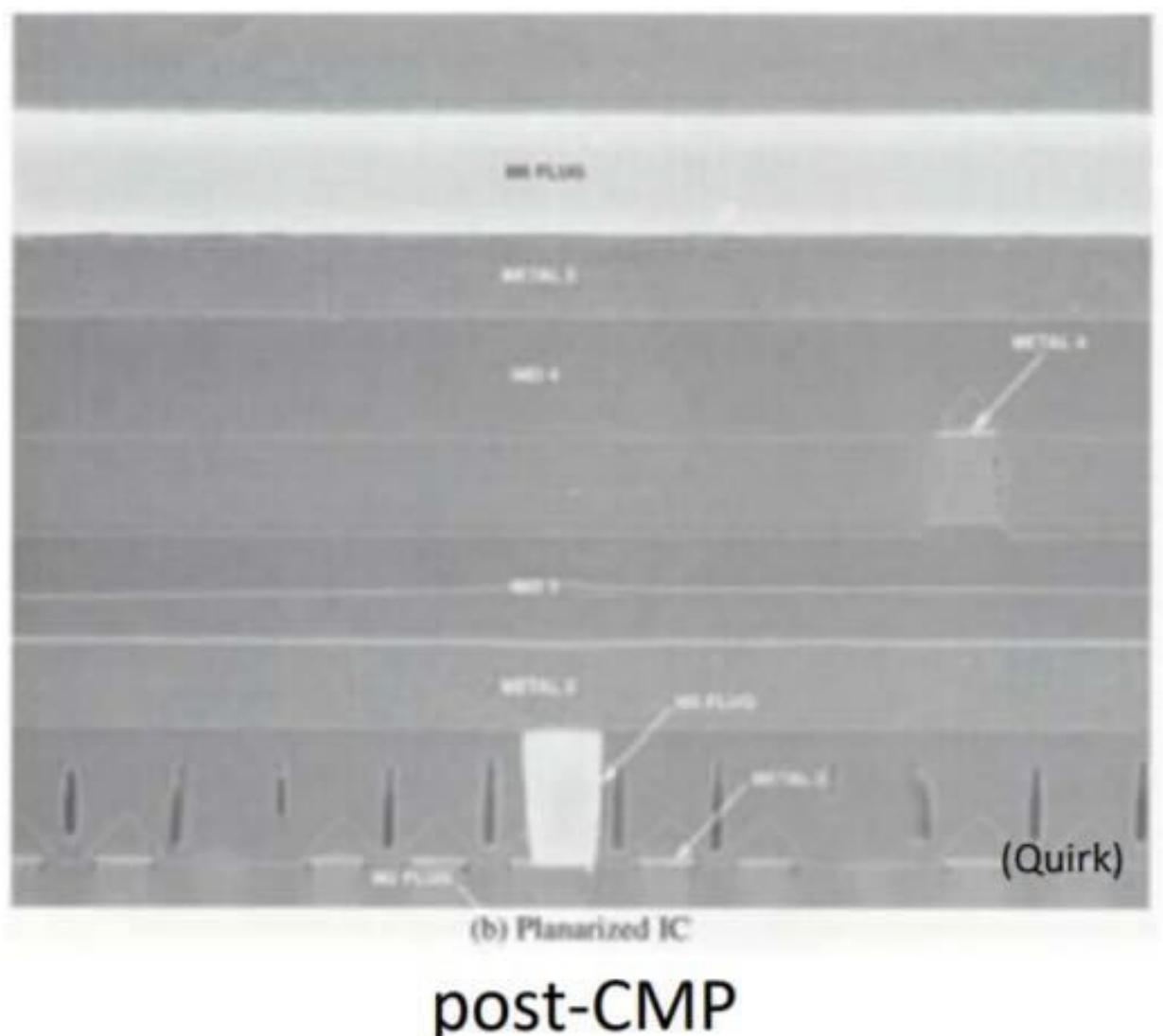

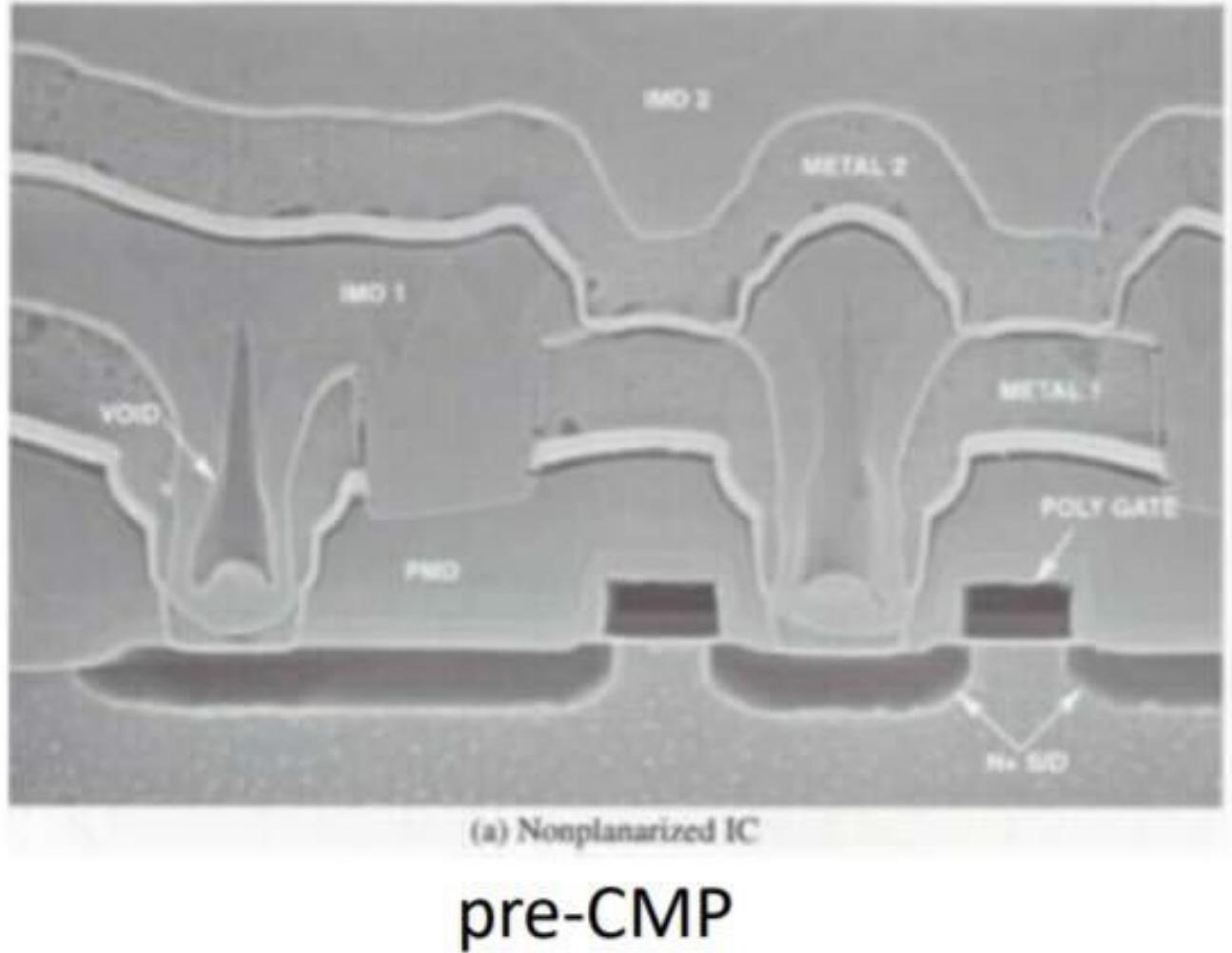

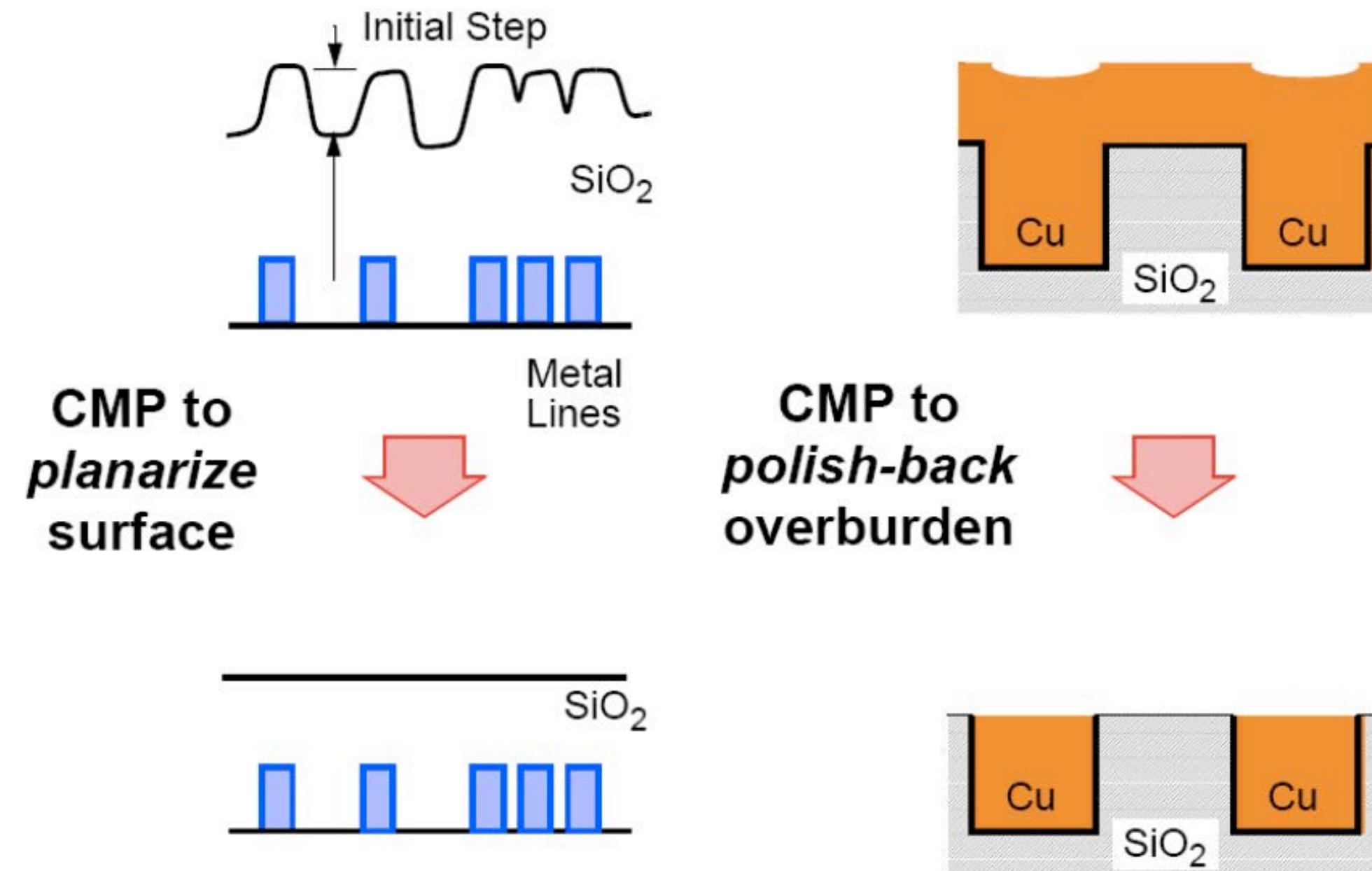

### Planarization

finer wavelength of light → shallower depth of focus

- after material addition, you do not have a flat surface

- these steps compound in height

- needs to be **really, really, really** flat for lithography

polishing is needed in order to flatten the wafer

- perfect for mechanical engineers!

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

### Planarization

finer wavelength of light → shallower depth of focus

- after material addition, you do not have a flat surface

- these steps compound in height

- needs to be **really, really, really** flat for lithography

polishing is needed in order to flatten the wafer

- perfect for mechanical engineers!

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

31

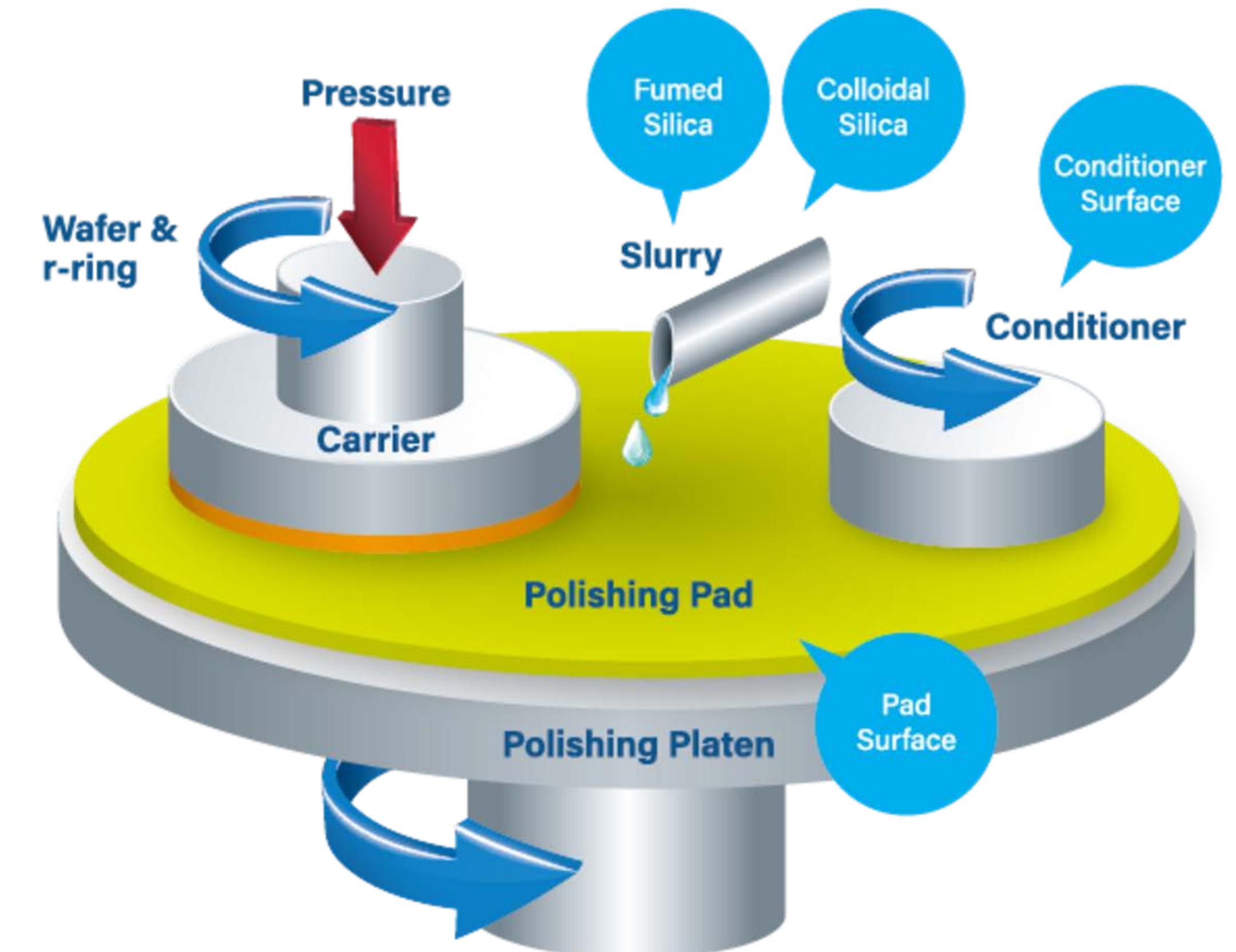

### Chemical Mechanical Polishing

silicon is hard, and e.g. copper is relatively softer

- balancing act: polish both without over/under polishing

slurry: abrasive chemical suspended in a solution

pads: porous to hold slurry and supply mechanical energy

material removal: mechanical + chemical actions

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

32

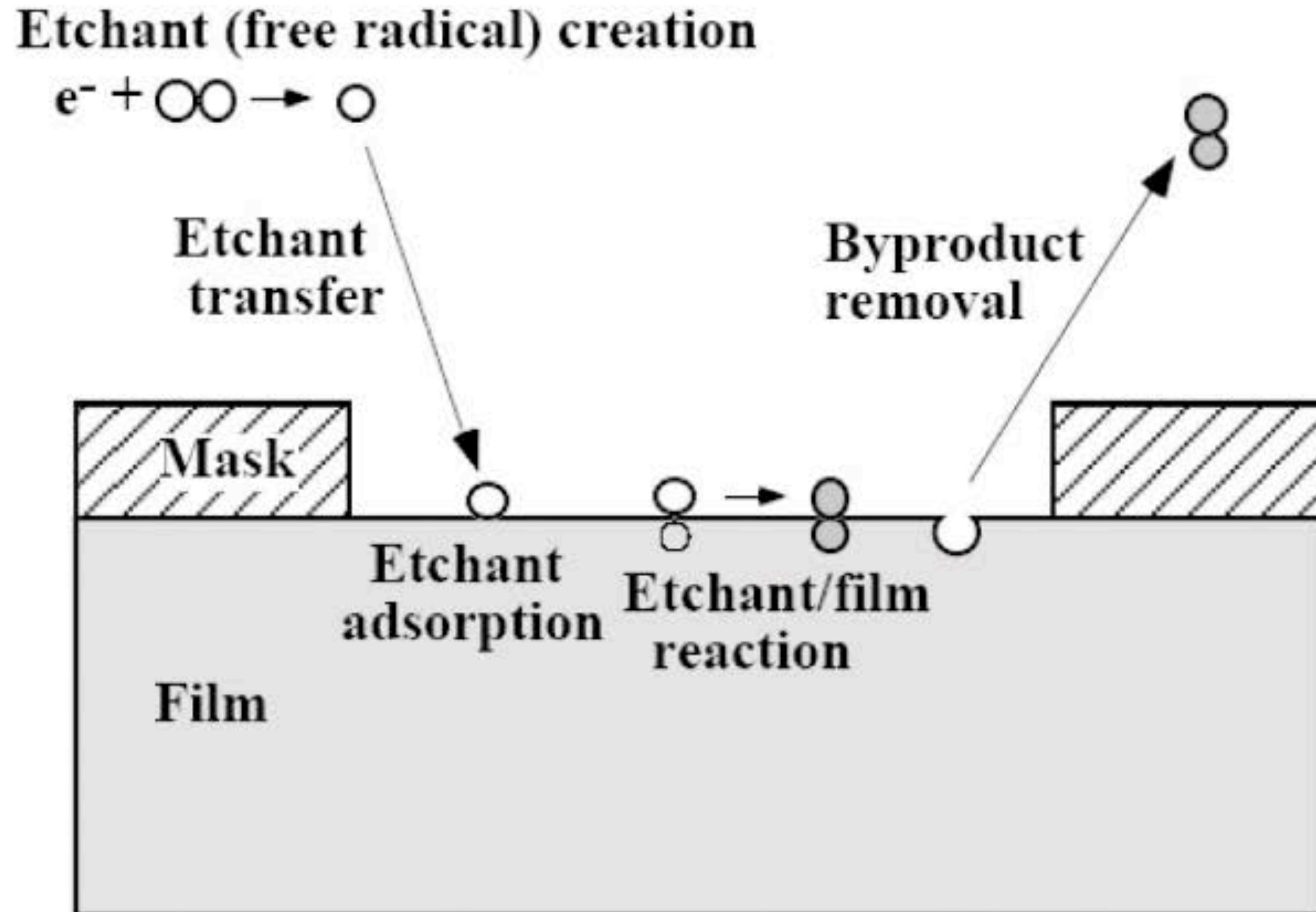

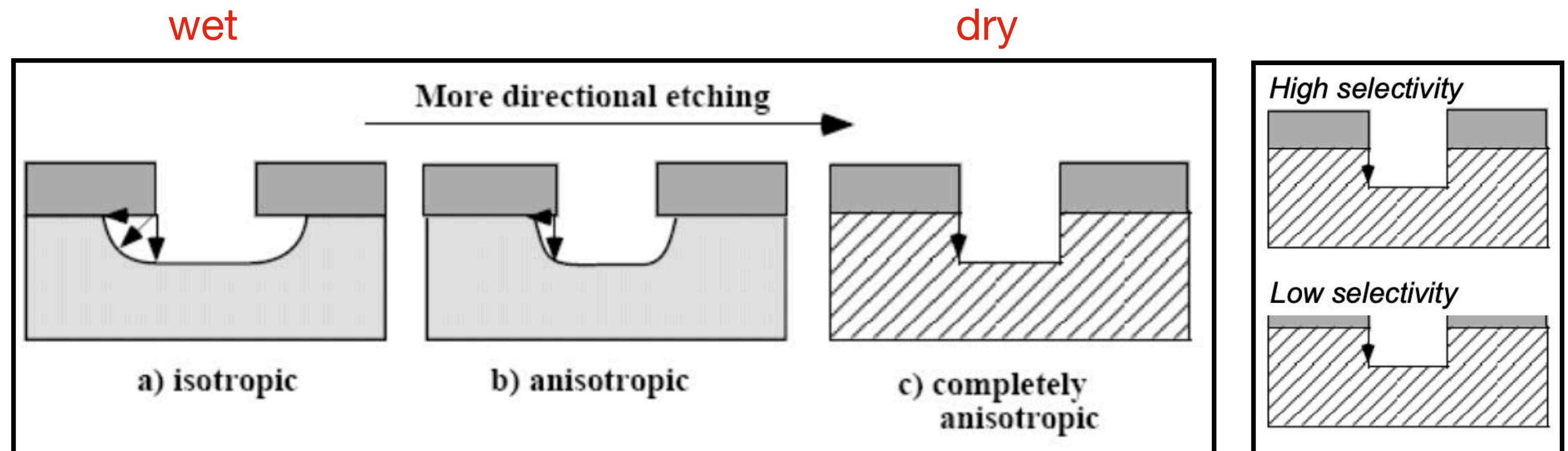

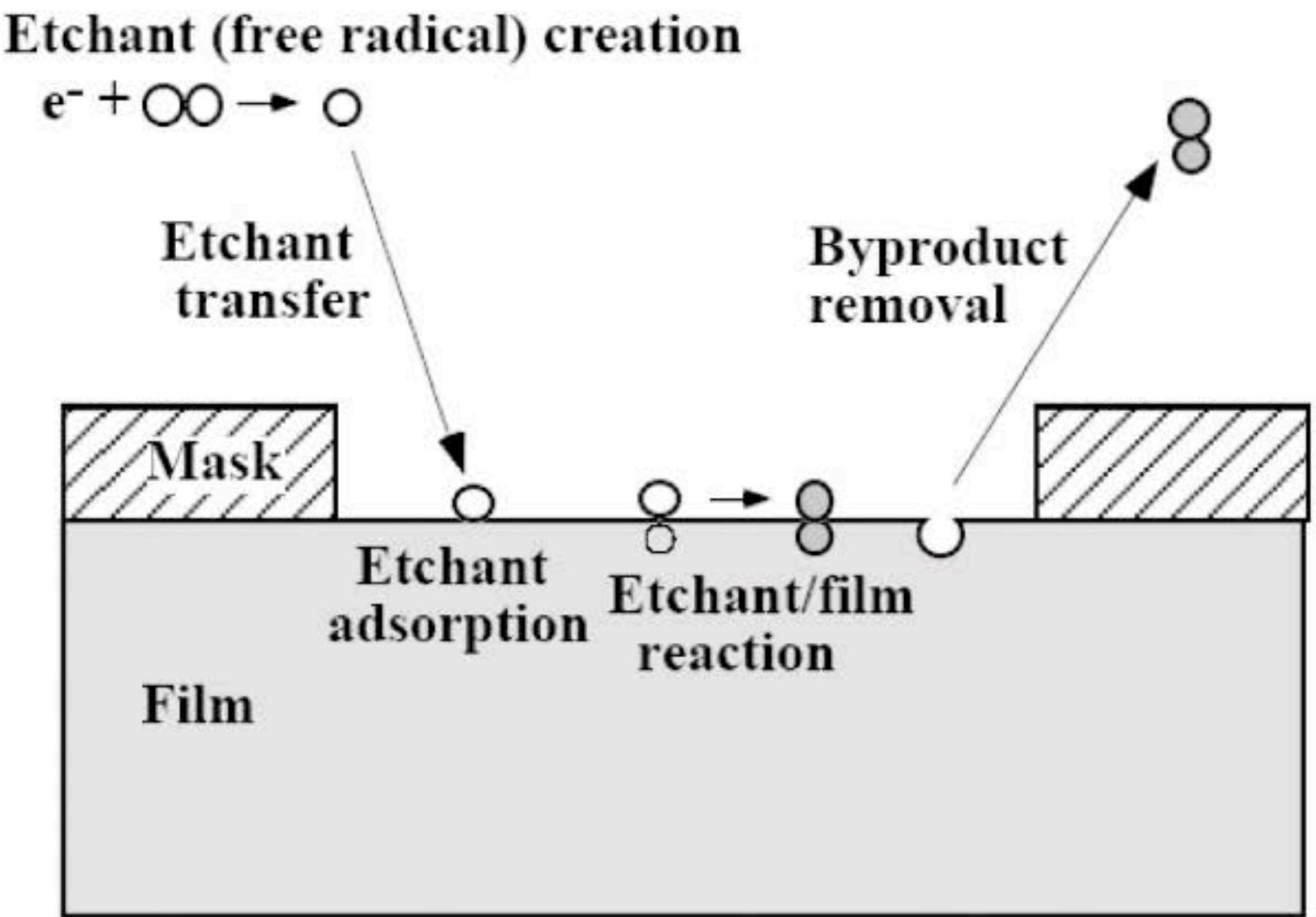

### Etching: Process

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

33

### Etching: Process

must figure out **selectivity**

(comes from chemistry)

and **directionality** (comes

from physical processes)

- want good control of both

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

34

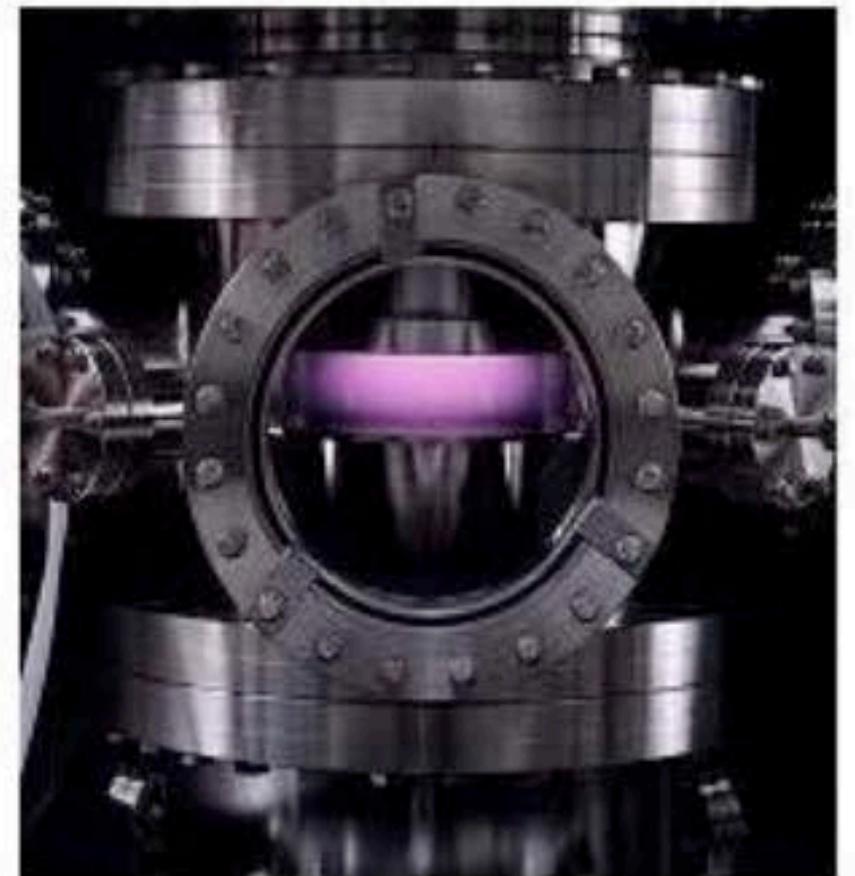

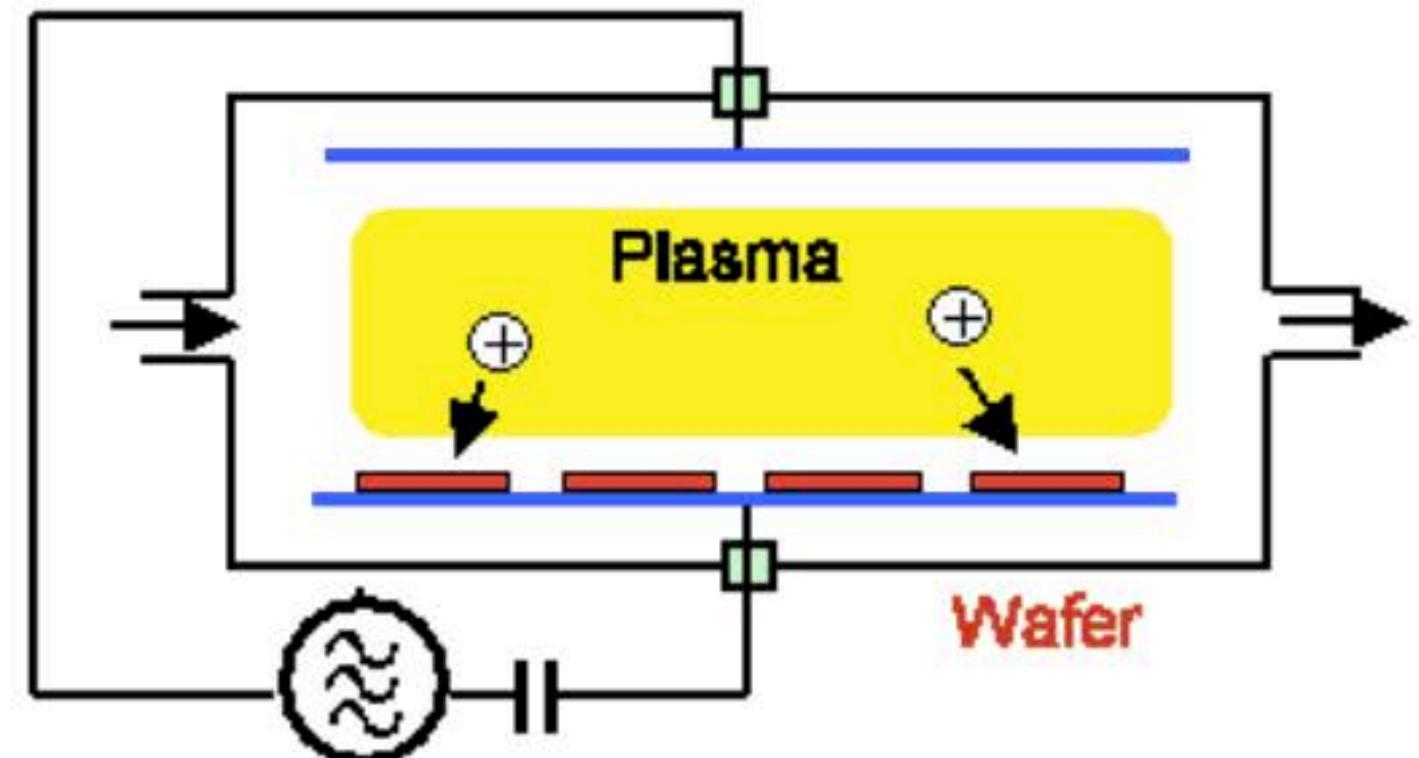

### Plasma Etch: Surface Chemistry

etching can be done **dry** or **wet**

- dry etching: use of plasma

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

35

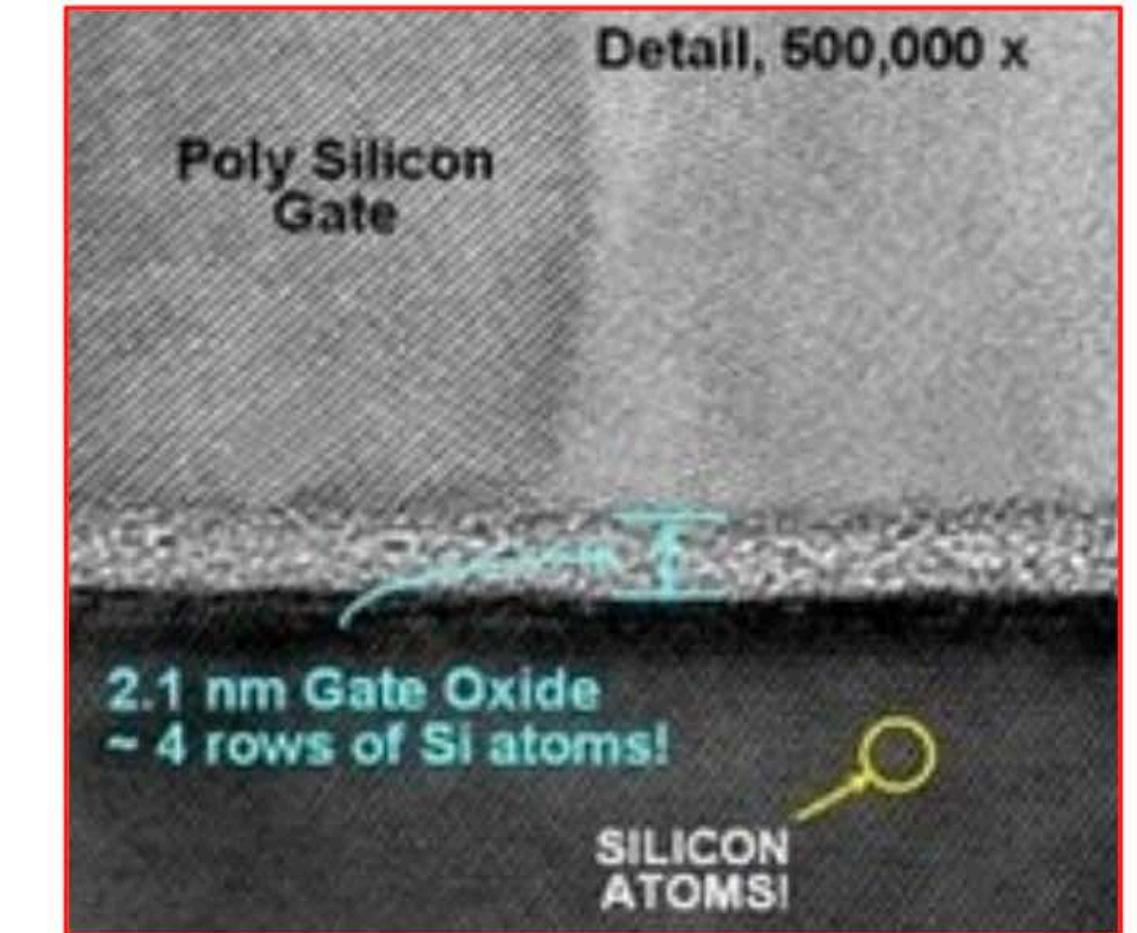

### Process Flow Example: Gate Oxidation

Gate: critical for electrical performance of the transistor

- need higher quality oxide than previous steps

- high purity from a well controlled process

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

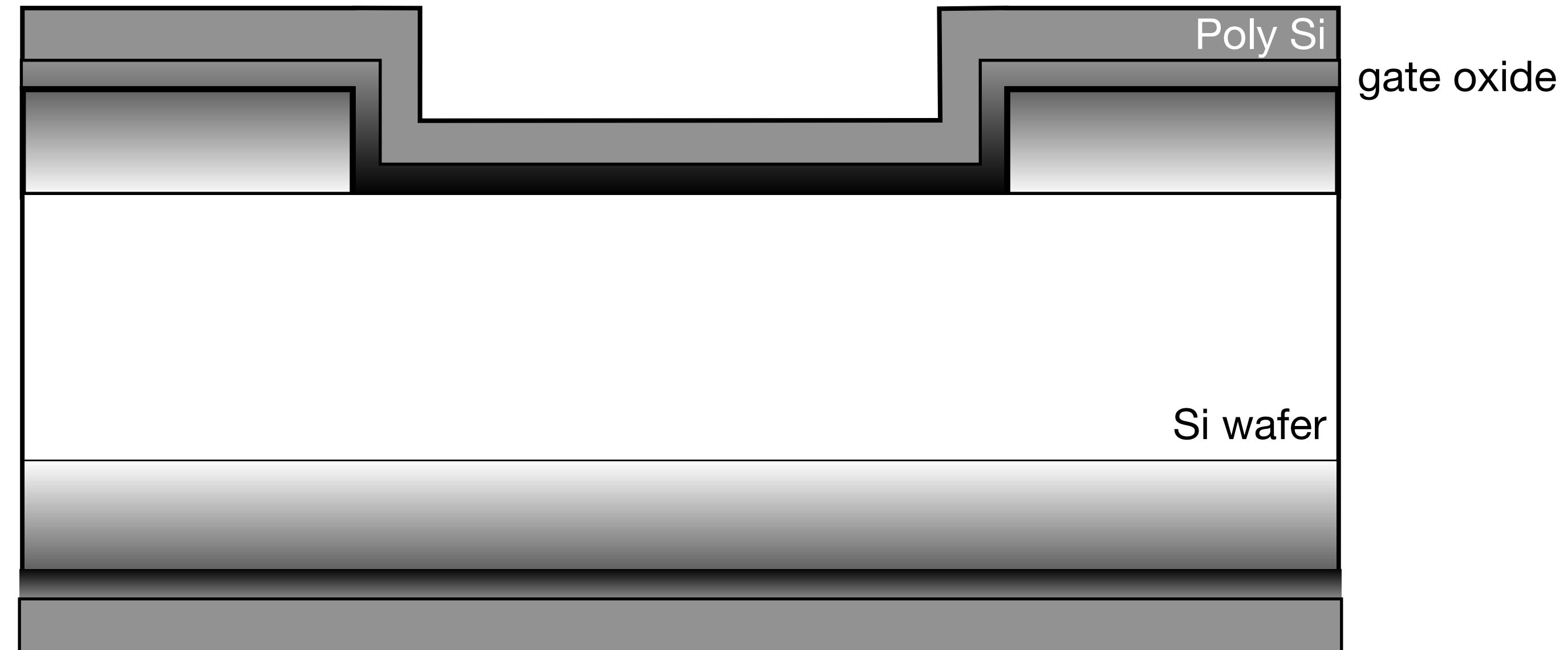

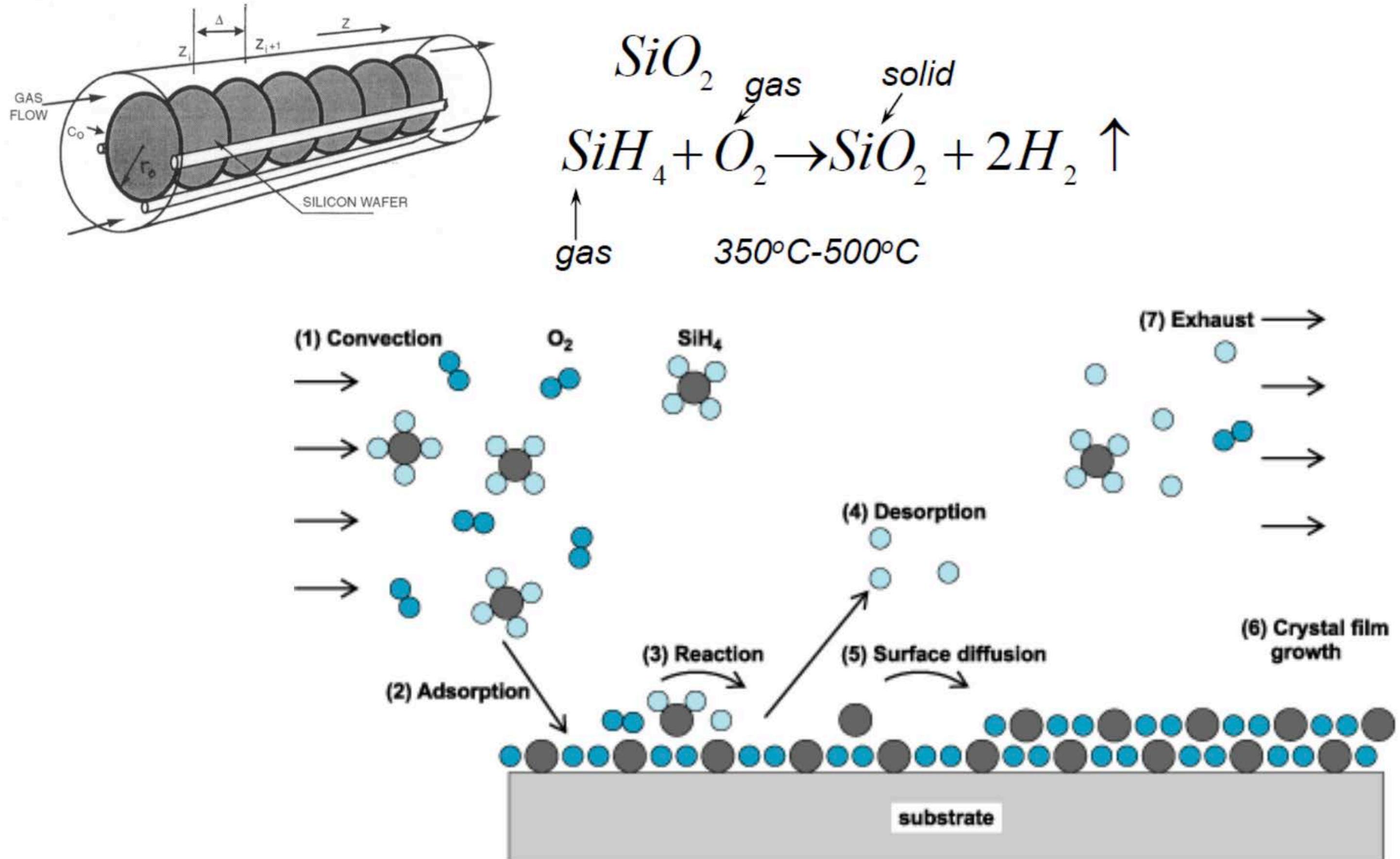

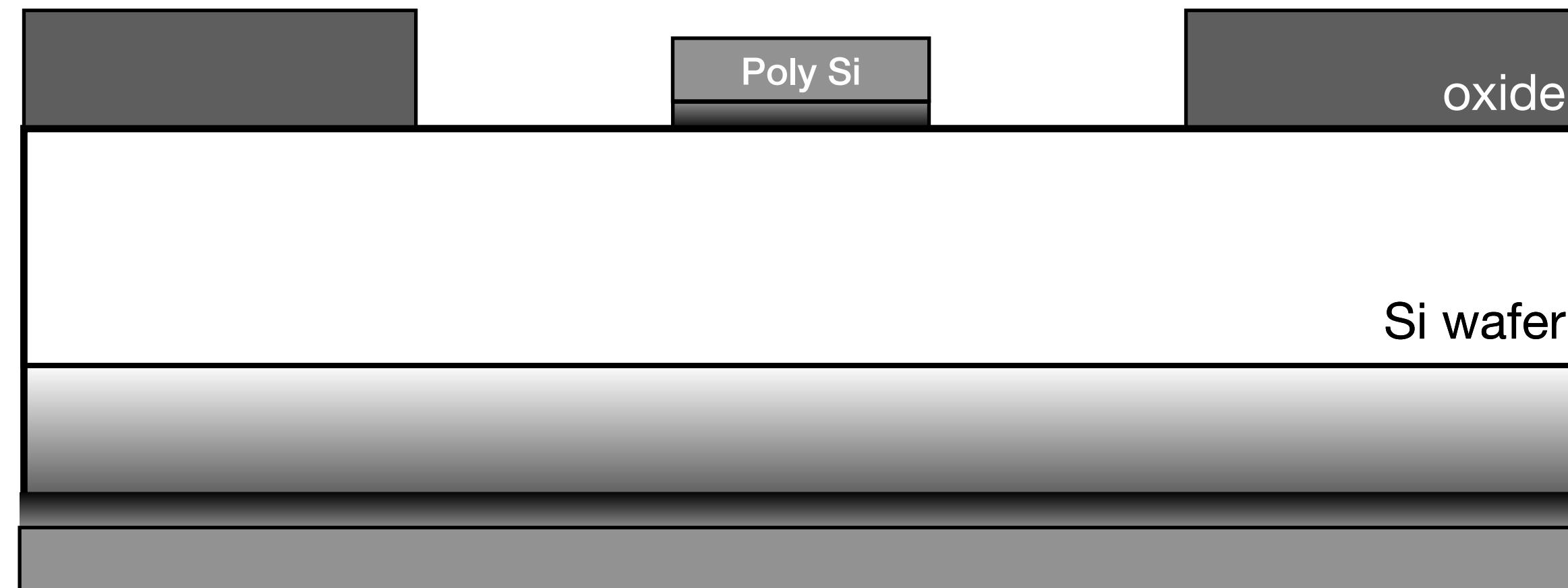

### Process Flow Example: Poly Si Deposition

#### Poly Si Deposition

- polycrystalline silicon: different material properties from starting wafer

- both Poly Si and Gate Oxide applied with CVD

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

37

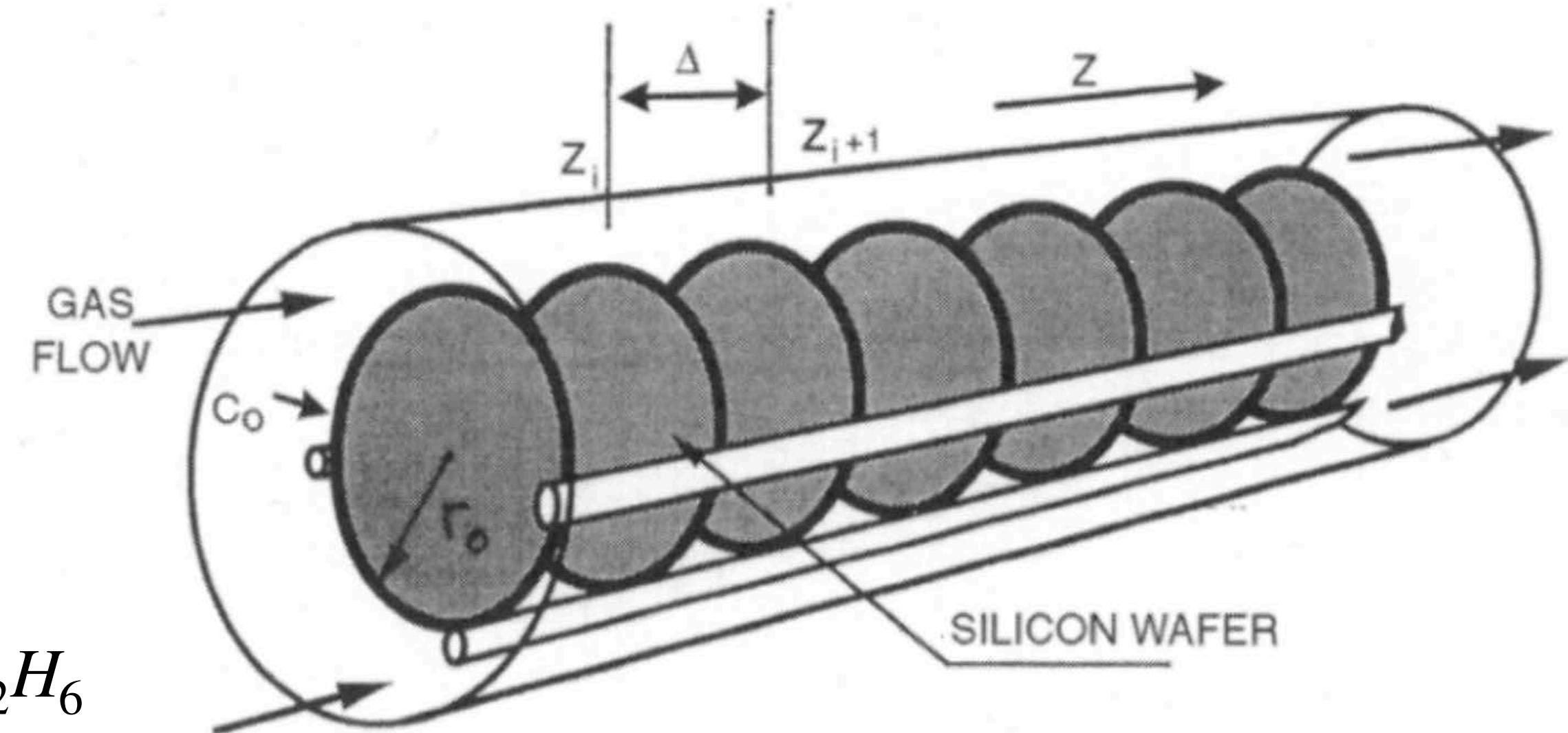

### Chemical Vapor Deposition

$SiH_4$

$N_2$

$HCl$

$H_2$

$PH_3, AsH_3, B_2H_6$

$H_2$

$SiCl_2$

$SiCl_4$

$SiH_2Cl_2$

$SiHCl_3$

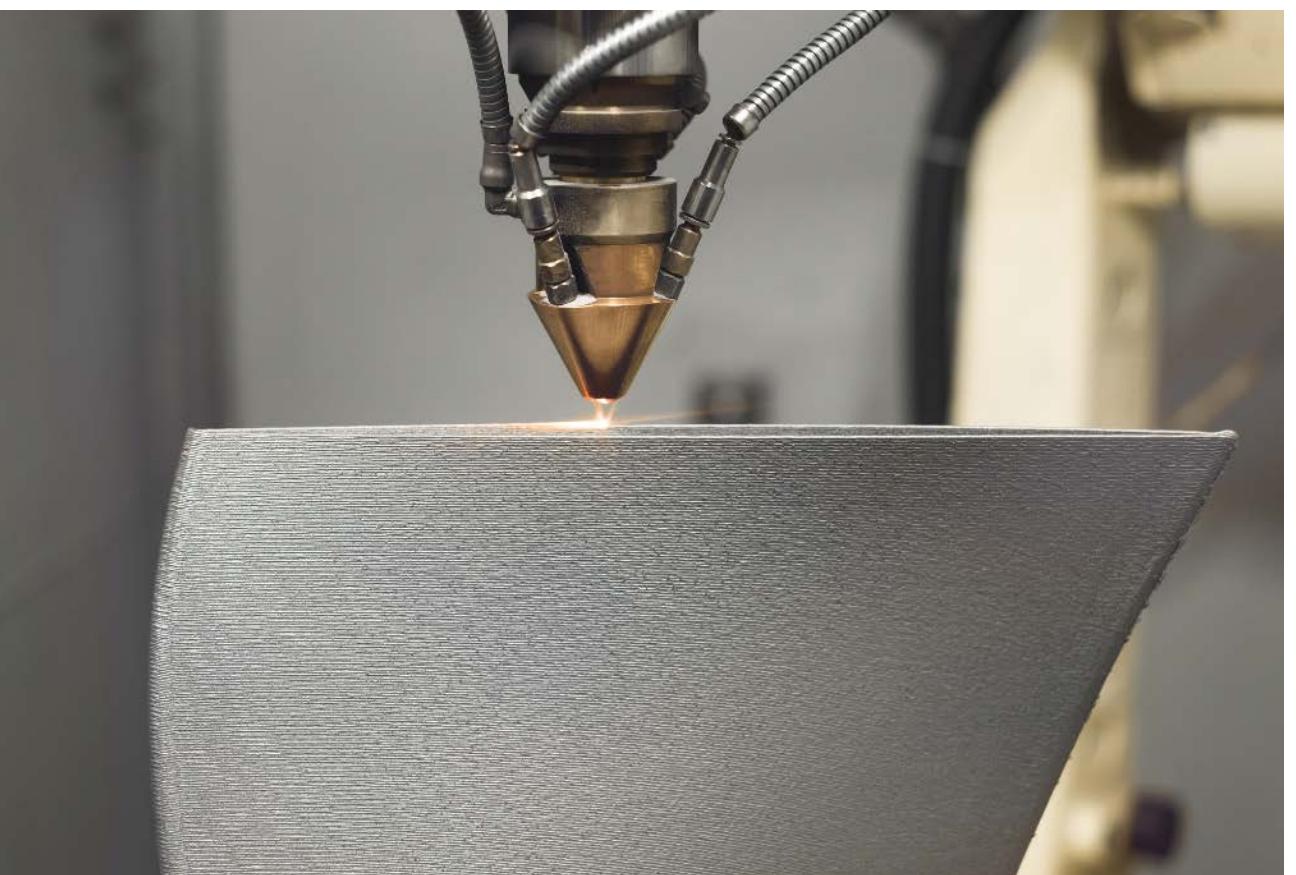

CVD: deposition method that uses a chemical reaction to deposit materials from gaseous precursors

- precursors: trade secrets 😊

- versatile

- conformal (coats surface)

- good for thicker coatings

PVD: deposition where a material (typically a metal) is vaporized and flows such that it can condense on the substrate

- good for thinner coatings

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

38

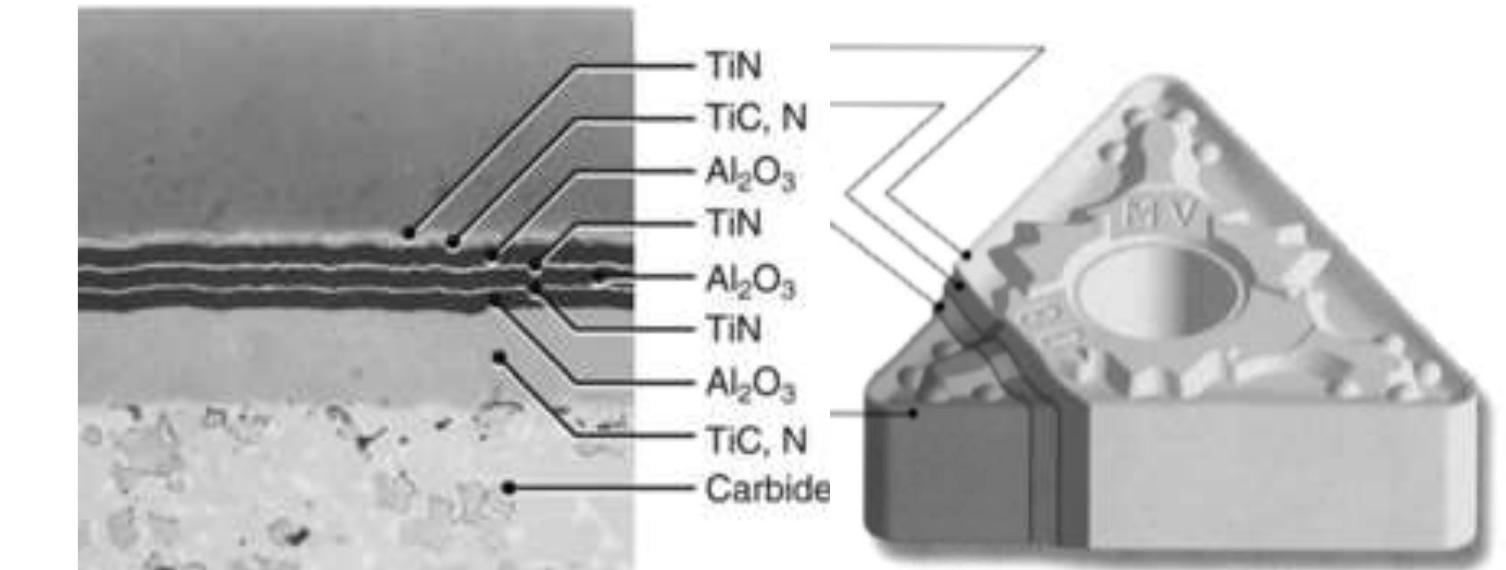

## Tool Coatings

- increase wear resistance

- increase oxidation resistance

- reduce friction

- increase resistance to metal fatigue

- increase resistance to thermal shock

**Layers: 2-20  $\mu\text{m}$  thick**

**TiN:** low friction

**TiCN:** wear resistance

**Al<sub>2</sub>O<sub>3</sub>:** high thermal stability

**Carbide:** hardness and fracture toughness

from DeGarmo's Materials & Processes in Manufacturing (10th Edition) by Black and Kohser, © Wiley (2008).

Kalpakjian and Schmid, Manufacturing Engineering and Technology.

from DeGarmo's Materials & Processes in Manufacturing (10th Edition) by Black and Kohser, © Wiley (2008).

## Examples:

- **TiN** (a basic yellowish coating that has fallen out of wide use)

- **TiCN** (a popular bluish-grey coating)

- **TiAlN and AlTiN** (an extremely popular dark purple coating)

- **TiAlCrN, AlTiCrN and AlCrTiN** (**PECVD** coating)

- **PCD:** polycrystalline diamond

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

39

### Chemical Vapor Deposition

**Generic:**  $2AB \text{ (gas)} \rightarrow 2A \text{ (solid)} + B_2 \text{ (gas)}$

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

40

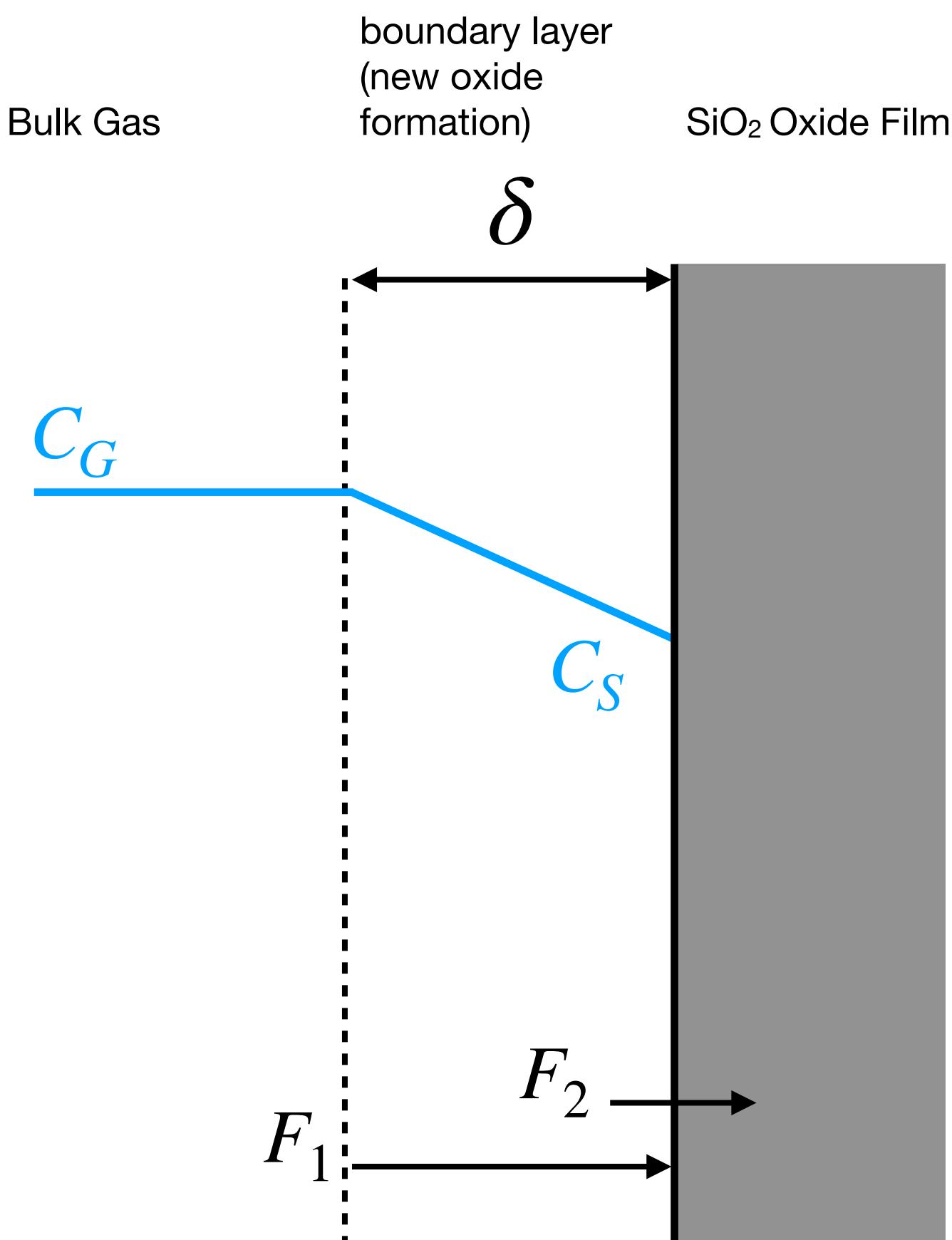

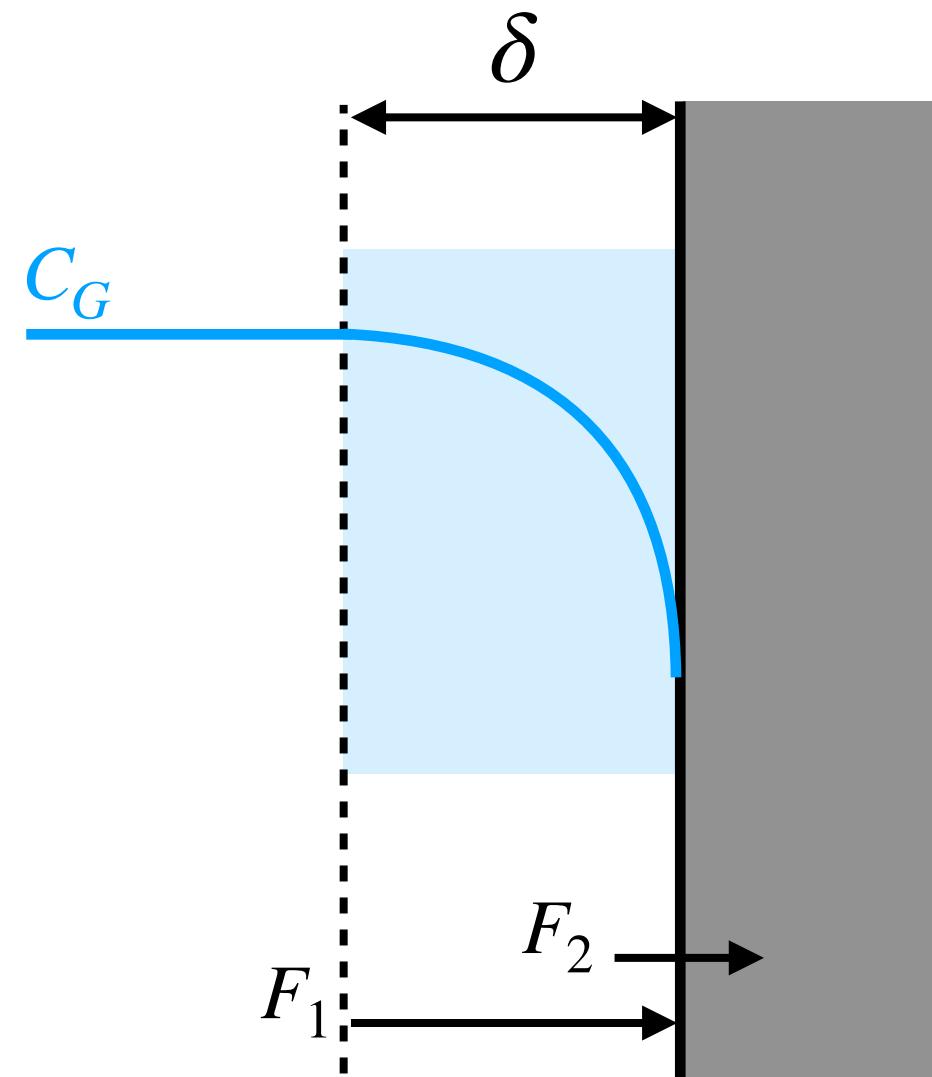

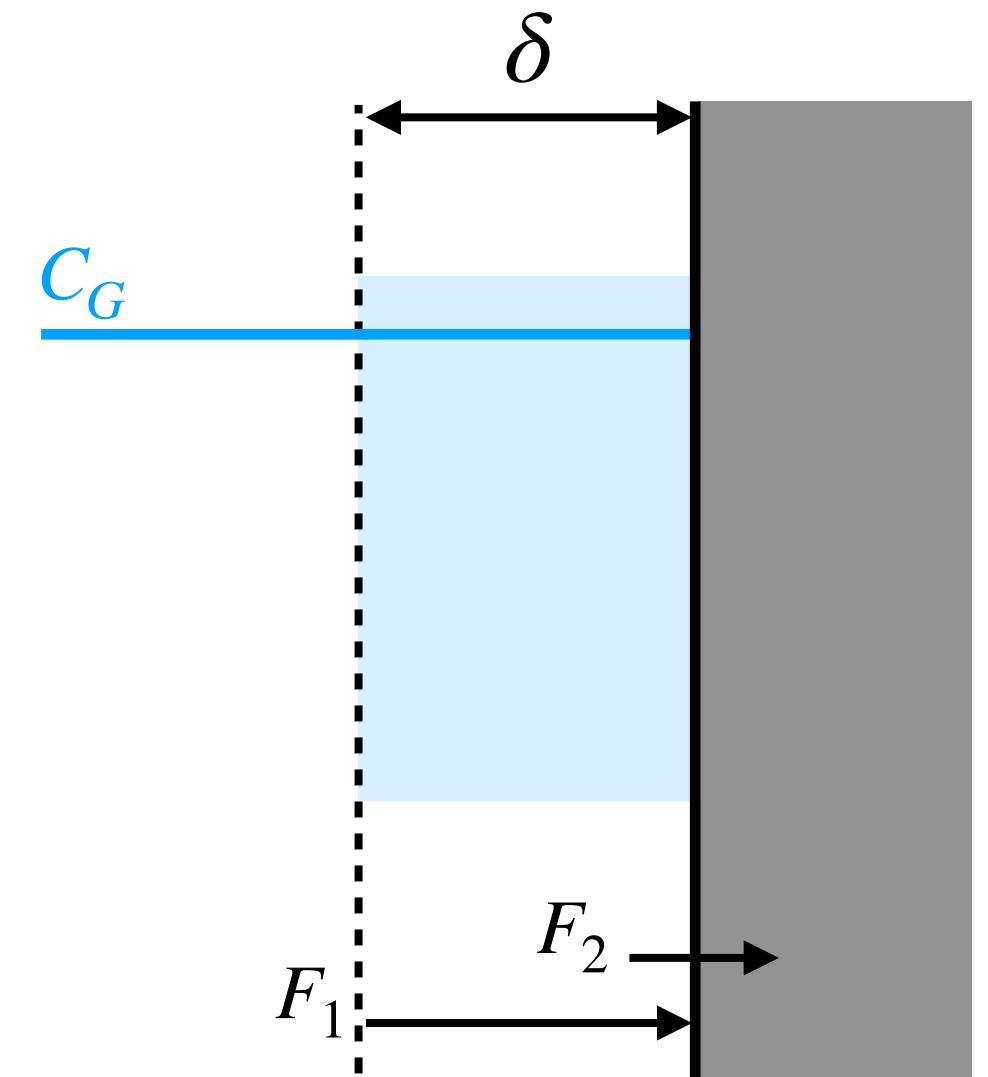

### Chemical Vapor Deposition: Rate (Diffusion vs Reaction)

“Deal-Grove Model”

Diffusion Flux  $F_1 = h_G(C_G - C_S)$

Reaction Flux  $F_2 = kC_S$

Steady State  $F_1 = F_2$

$$kC_S = h_G(F_G - C_S) \rightarrow C_S = \left( \frac{h_G}{k + h_G} \right) C_G$$

Growth Rate

$$v = \frac{kC_S}{N} = \frac{C_G k h_G}{N(k + h_G)}$$

h<sub>G</sub>: mass transfer coefficient (diffusivity of gas/δ)

C<sub>G</sub>: concentration of reactant (oxy) in bulk gas

C<sub>S</sub>: concentration of reactant in surface gas

k: reaction rate coefficient

v: growth rate

N: atomic density, N<sub>Si</sub>=5x10<sup>22</sup> atoms/cm<sup>3</sup>

ΔH: activation energy

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

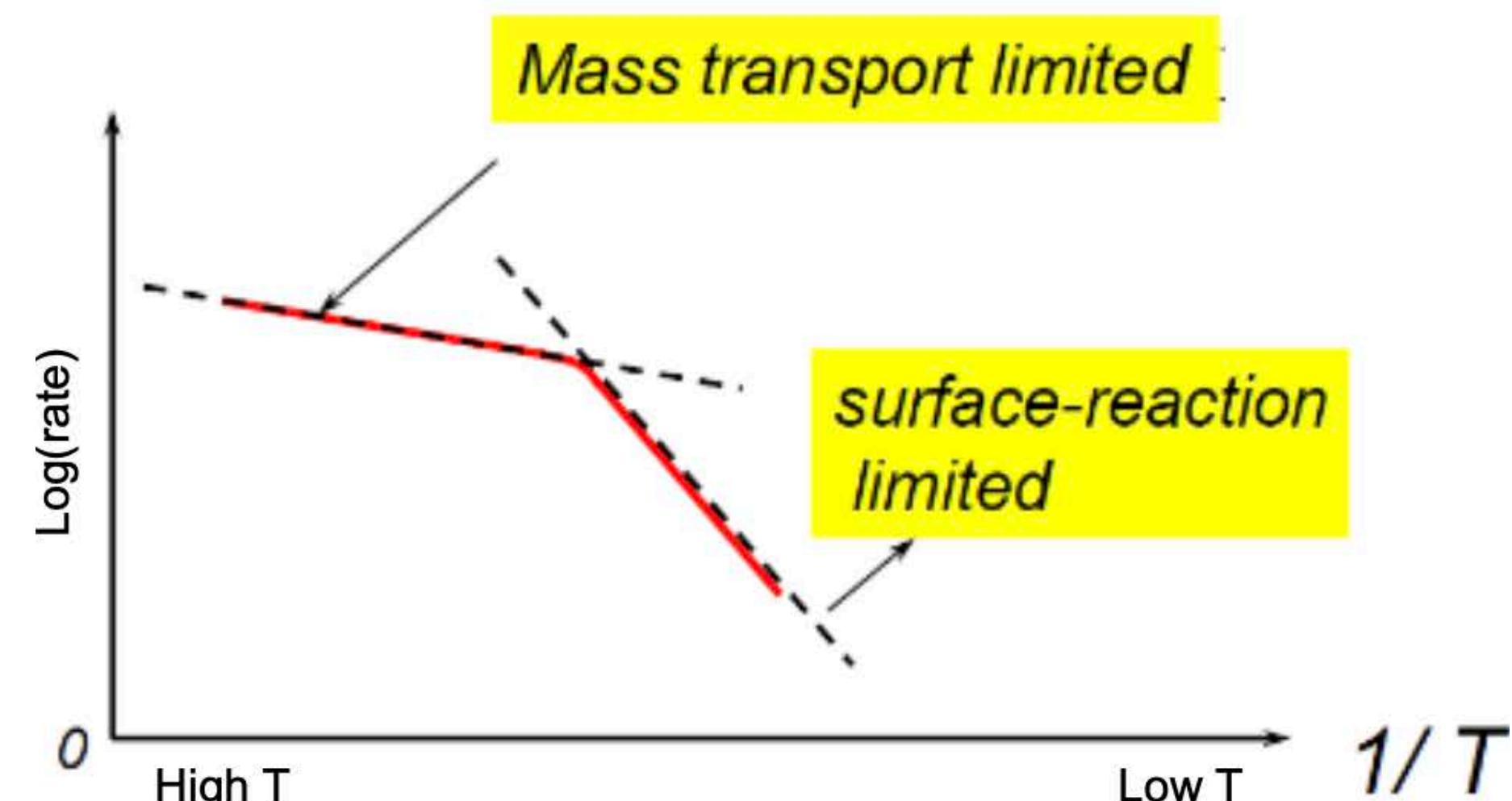

### Chemical Vapor Deposition: Rate (Diffusion vs Reaction)

Diffusion Limited

$$k \gg h_G$$

$$v = \frac{h_G C_G}{N} \propto T^{\frac{3}{2}}$$

Reaction Limited

$$k \ll h_G$$

$$v = \frac{k C_G}{N} \propto e^{\frac{-\Delta H}{kT}}$$

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

42

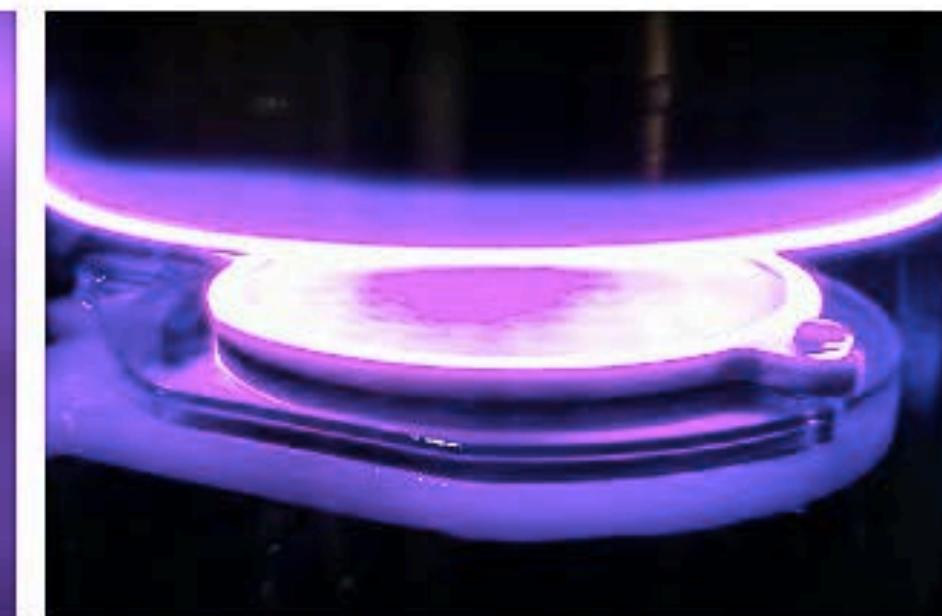

### Chemical Vapor Deposition: Plasma

allows for increase in Rate without increasing temperature

- non-thermal plasma: electron temperature high while the rest of the gas is at a lower temperature

- no damage to the existing structure

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

43

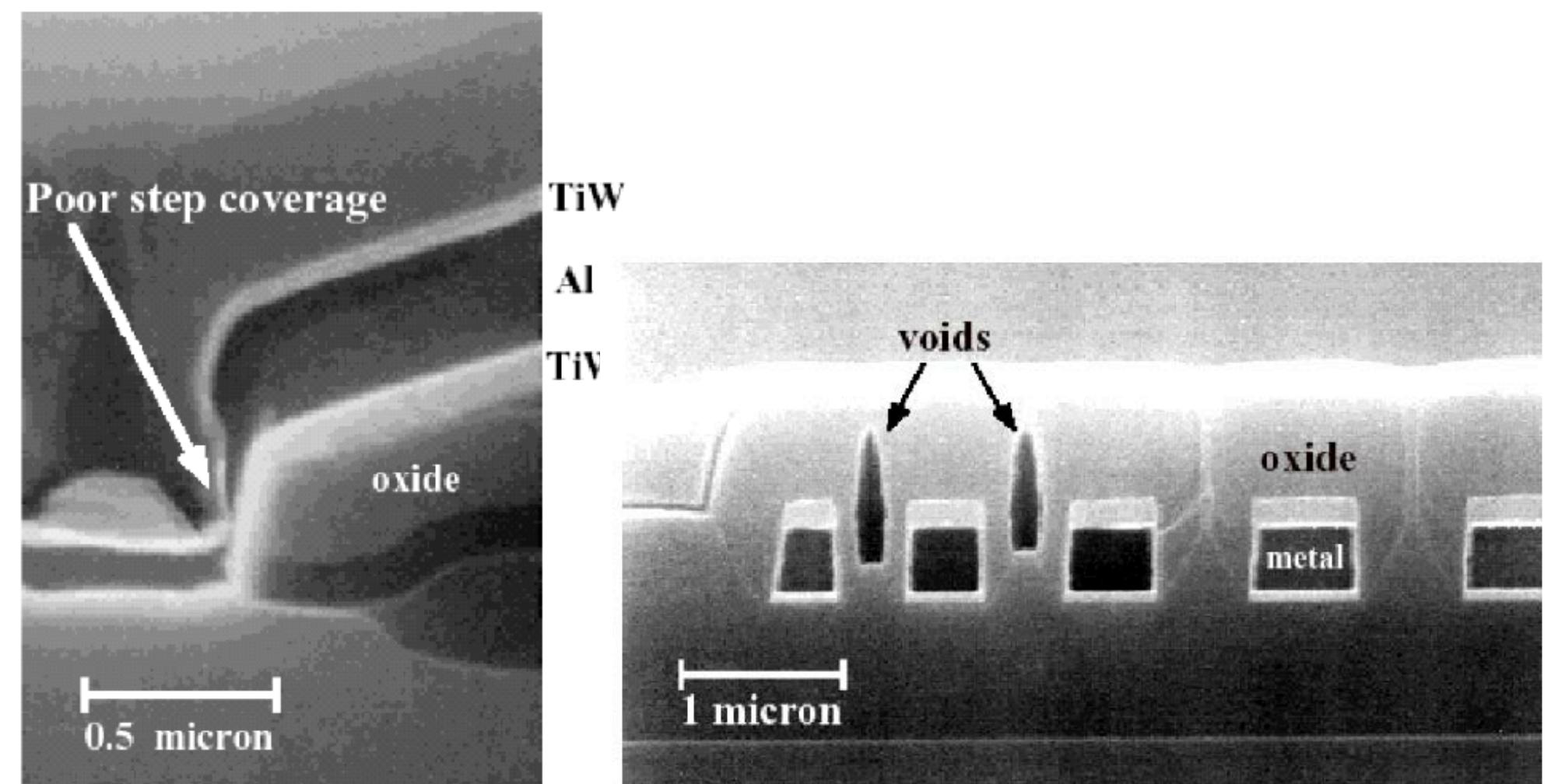

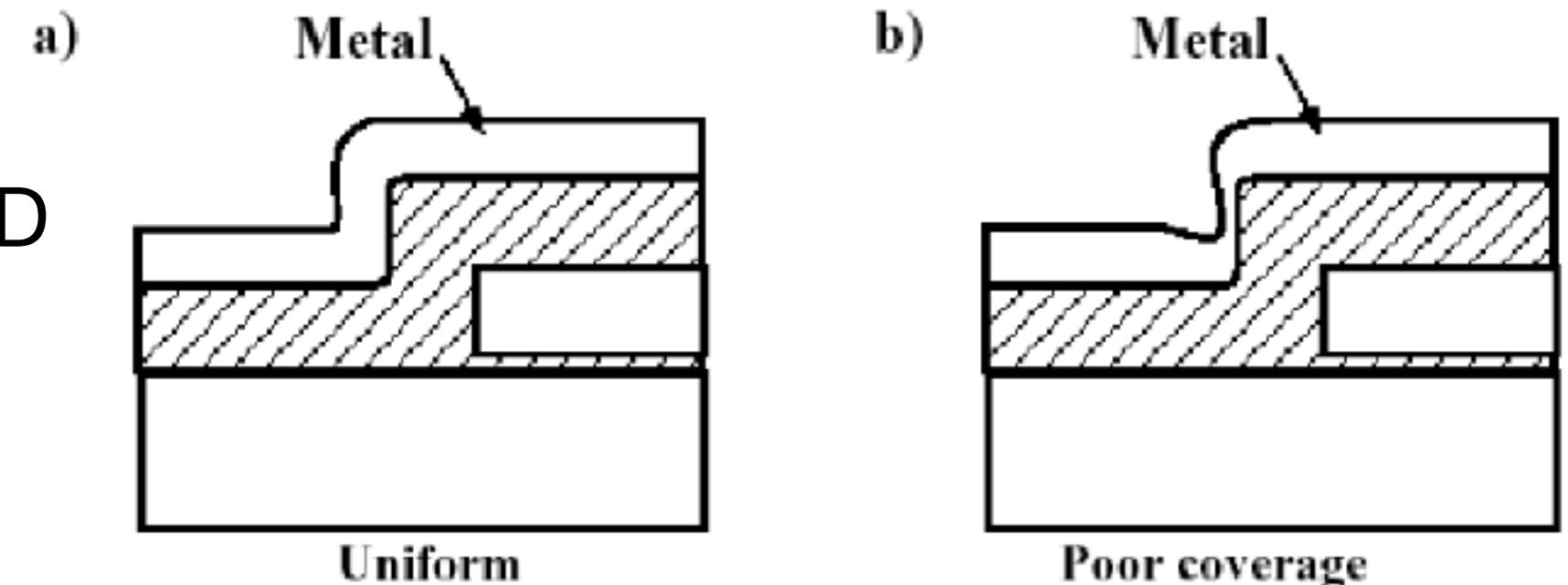

### Chemical Vapor Deposition

#### Process Parameters

- temperature

- total pressure

- partial pressure of reactants

- flow rate of reactants and carrier gases

- time

#### Control Parameters

- film thickness (~1-1000 nm and getting thinner - atomic layers)

- film deposition rate

- poly silicon: ~hundreds nm/min

- silicon dioxide: 10-100 nm/min

- aluminum: 10s of nm/min

- film uniformity and quality

#### Quality

- better step coverage than PVD

- better for high aspect ratios

- void issues due to inconsistency/directionality

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

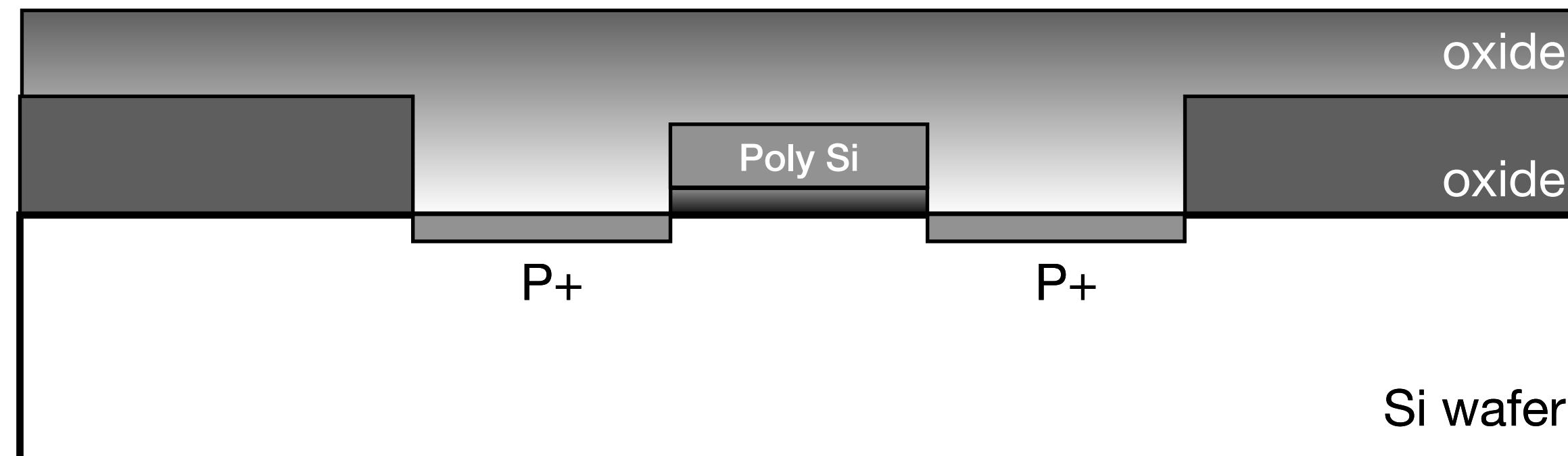

### Process Flow Example: Pattern Poly Si

#### Pattern Poly Si

- deposit photoresist and develop

- dry etch poly Si

- remove photoresist

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

45

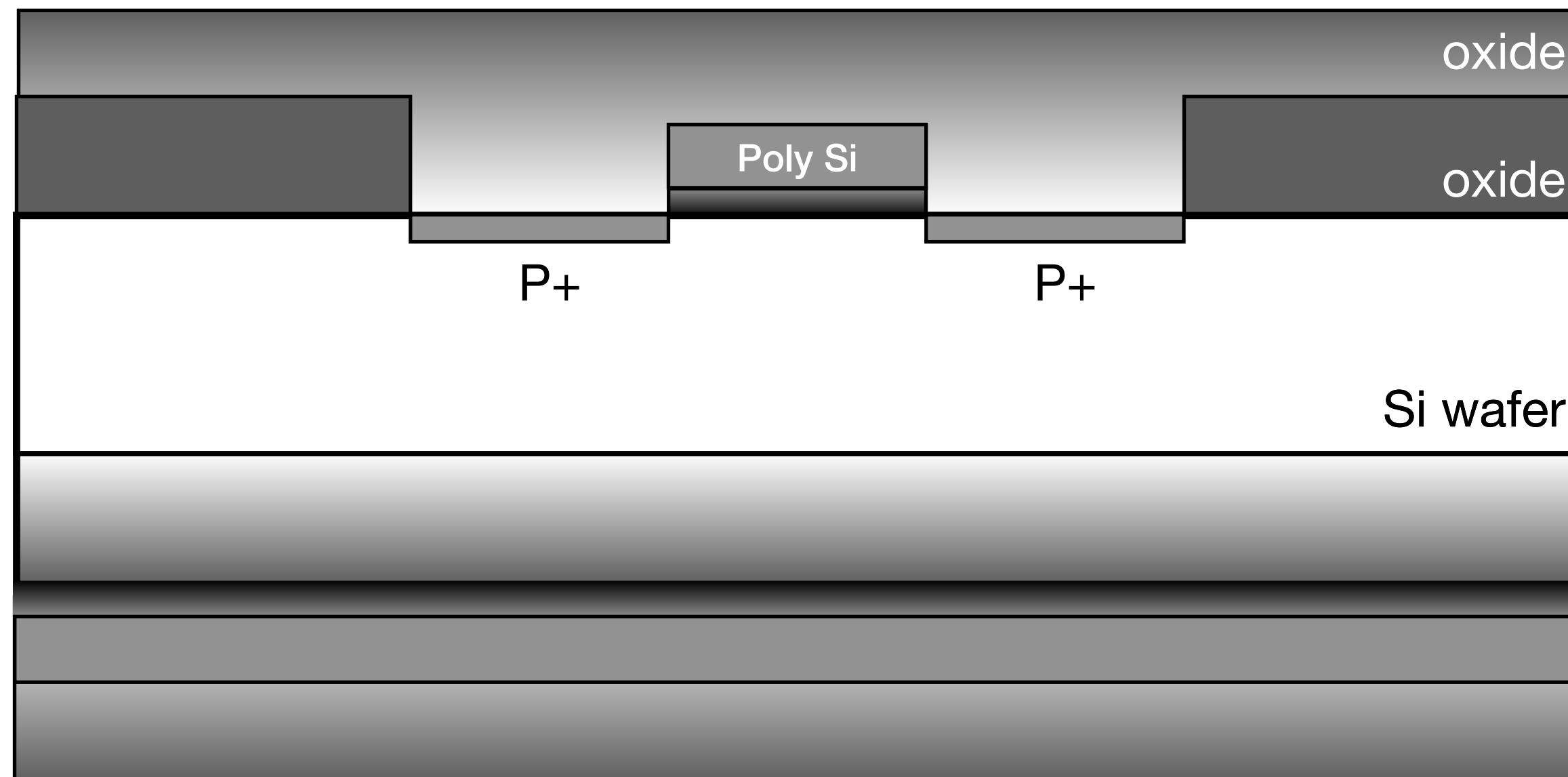

### Process Flow Example: P+ Ion Implantation

Poly Si acts as a mask

P+ Ion Implantation

- Source/Drain P+ diffusion (tune electrical properties)

Reoxidation: fill in gaps and protect with a “roof”

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

46

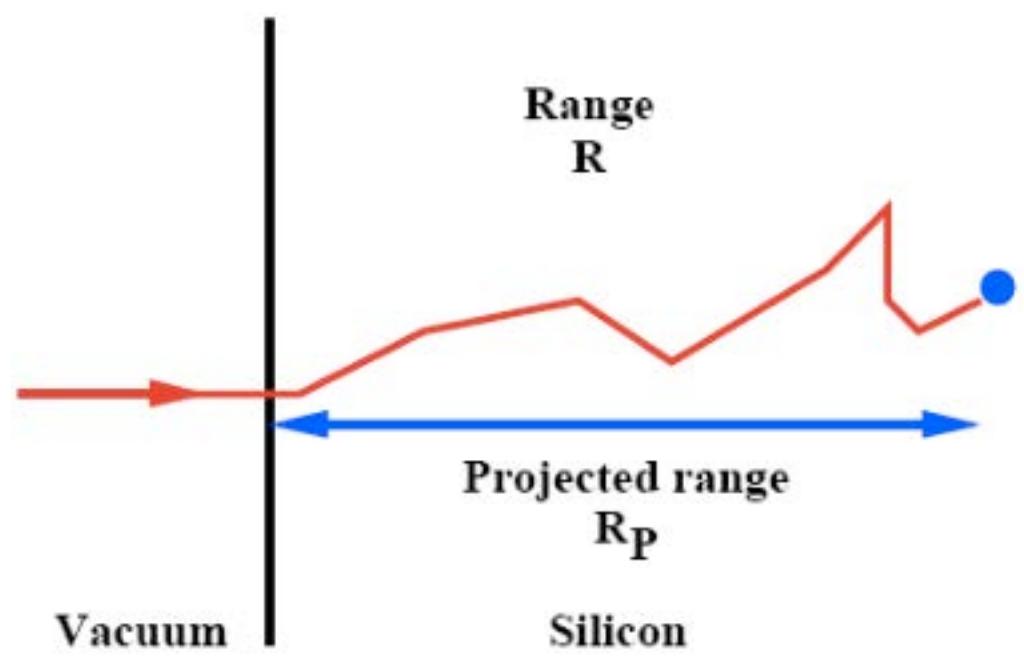

### Ion Implantation

Random process: like shooting a gun of ions at a wall (silicon matrix)

- high energy (1-1000keV) ions bombard the substrate and lose energy through nuclear collisions and electronic drag forces

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

47

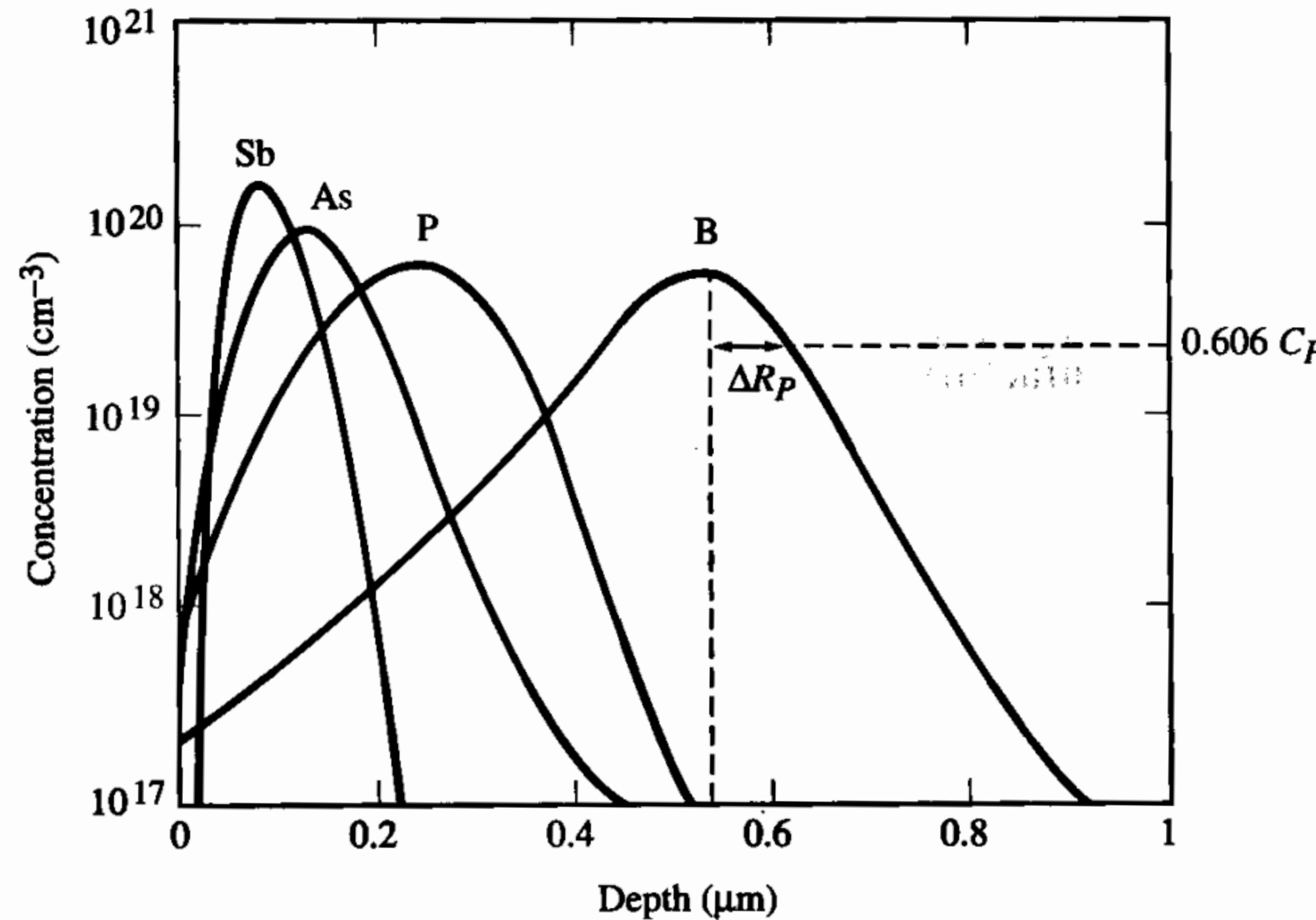

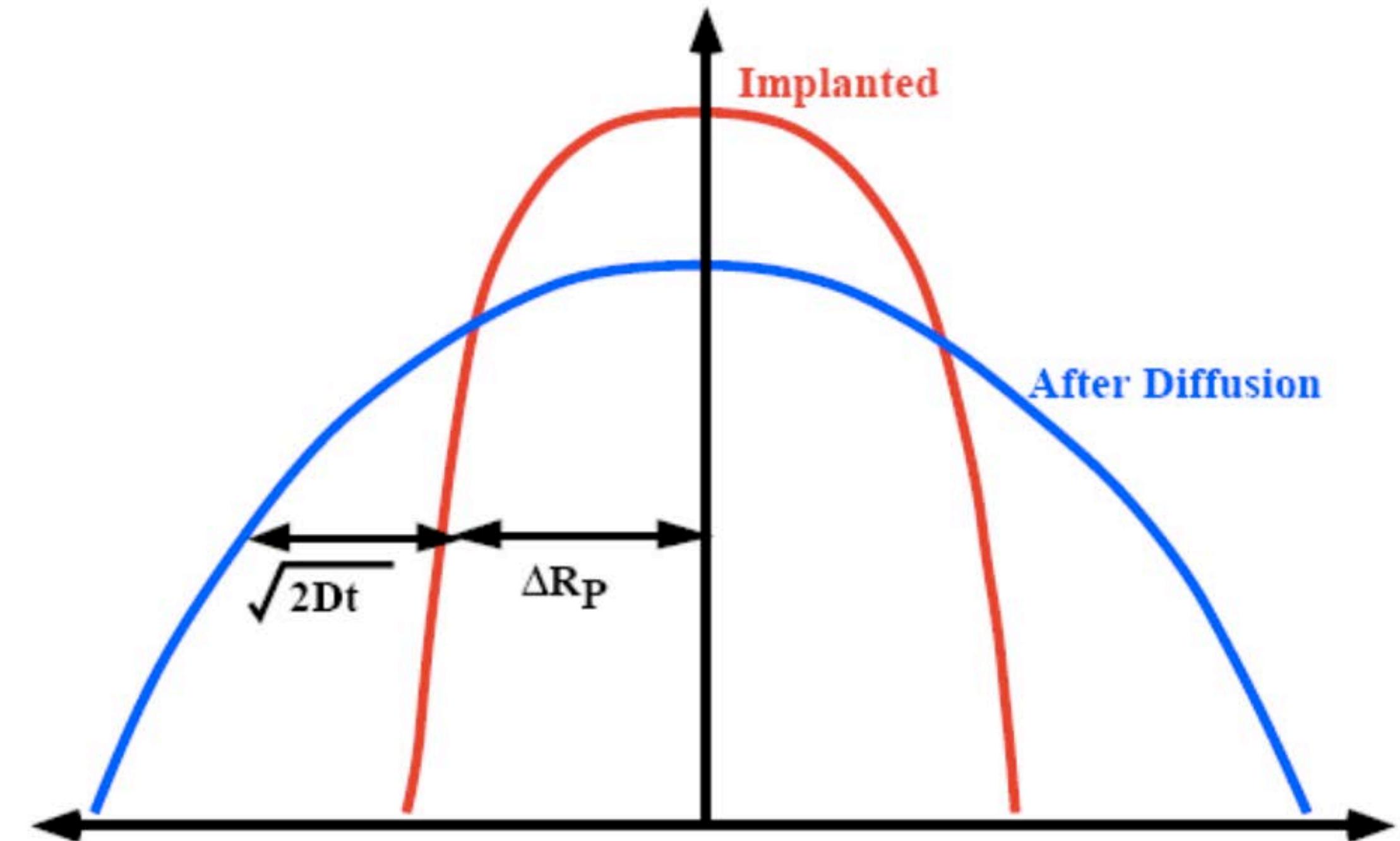

### Ion Implantation

Normal Distributions!

- concentration vs depth into the silicon substrate

- standard deviation: called “straggle”

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

48

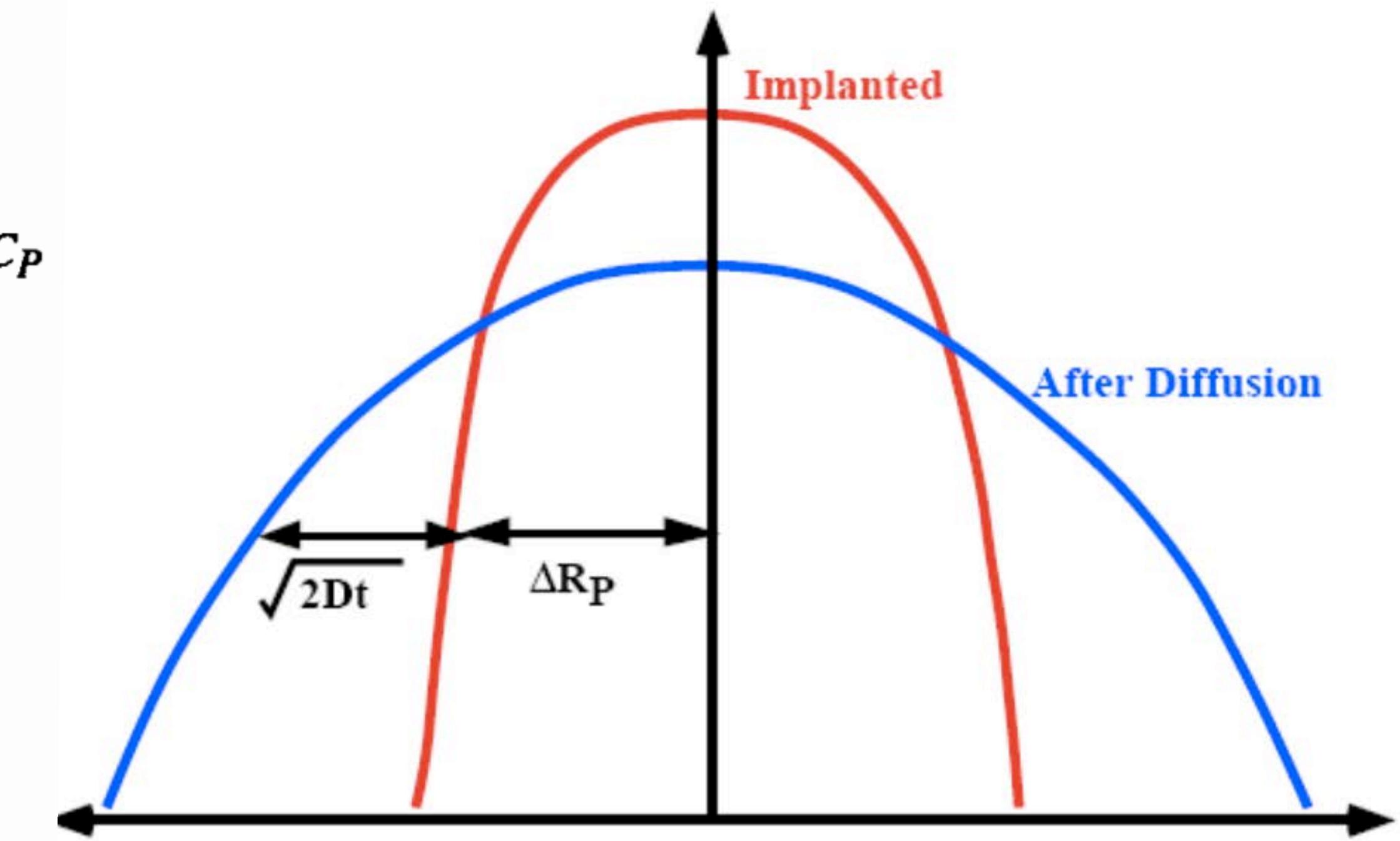

### Ion Implantation

$$C(x) = C_P e^{-\frac{(x - R_P)^2}{2\Delta R_P^2}} \quad \text{before annealing}$$

$$Q = \int_{-\infty}^{\infty} C(x) dx \rightarrow \sqrt{2\pi} \Delta R_P C_P$$

$$C(x, t) = \frac{Q}{\sqrt{2\pi(\Delta R_P^2 + 2Dt)}} e^{-\frac{(x - R_P)^2}{2(\Delta R_P^2 + 2Dt)}}$$

C: concentration of ions

Q: ion dose

C<sub>p</sub>: peak concentration

R<sub>p</sub>: average projected range

ΔR<sub>p</sub>: standard deviation or straggle

D: diffusion coefficient

t: annealing time

after annealing

Normal Distributions!

- concentration vs depth into the silicon substrate

- standard deviation: called “straggle”

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

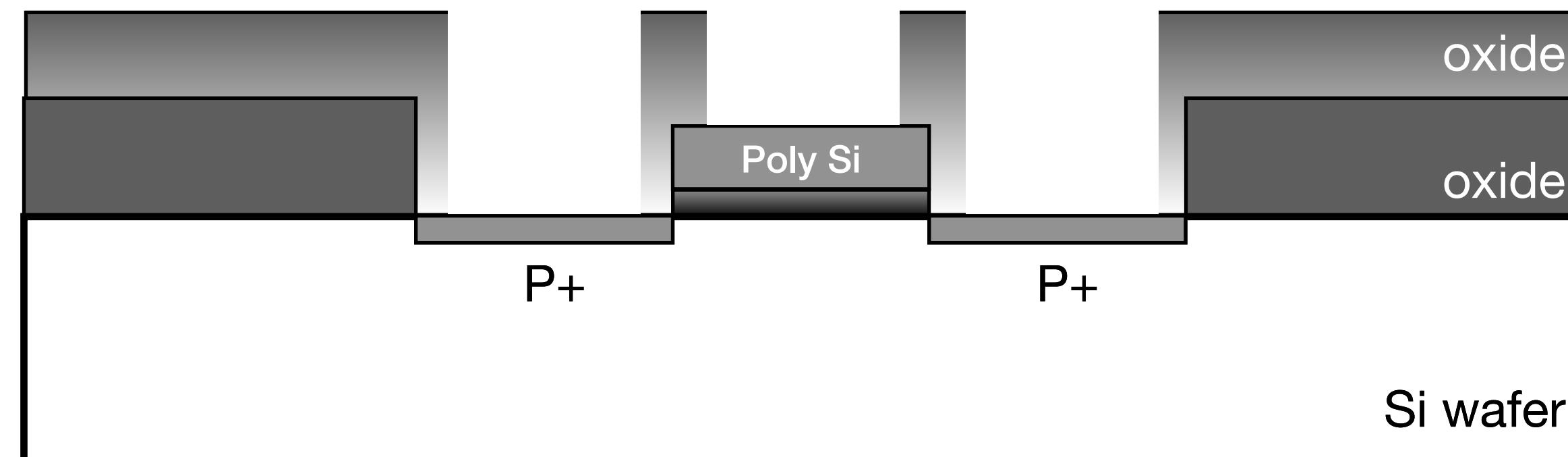

### Process Flow Example: Back Cleanup

Remove Oxide and Poly Si from back

- Oxide: BOE (Buffered Oxide Etch)

- Poly Si: Plasma etch

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

50

### Process Flow Example: Pattern Al Interconnects

Planarization

Apply photoresist, expose, develop

Oxide etching

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

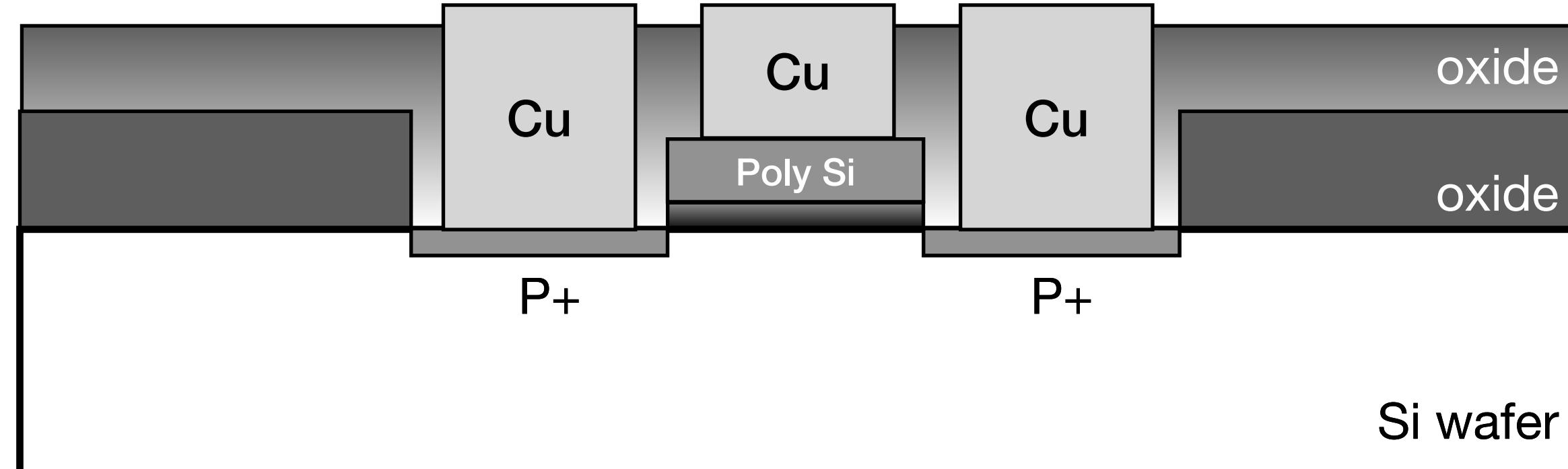

### Process Flow Example: Al Metallization

Hydrofluoric Acid dip to strip oxide layer

- add copper layer

Done! Until you add more layers...

- treat these processes like a “tool kit”

- library of processes to use to make different devices

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

52

## Manufacturing Attributes

Same stuff, different lingo

- production rate → throughput

- 300,000 cars/year vs 60 wafers/hour

- yield: takes the until you are at production levels

- don't throw away lower performing chips

- cost of ownership: how much it costs to produce a chip or feature

|                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <br><a href="#">See more images</a><br><br><b>Intel - Core i9-14900K 14th Gen</b><br>24-Core 32-Thread - 4.4GHz<br>(6.0GHz Turbo) Socket LGA 170... | <br><a href="#">See more images</a><br><br><b>Intel - Core i7-14700K 14th Gen</b><br>20-Core 28-Thread - 4.3GHz<br>(5.6GHz Turbo) Socket LGA 170... | <br><a href="#">See more images</a><br><br><b>Intel - Core i5-14600K 14th Gen</b><br>14-Core 20-Thread - 4.0GHz<br>(5.3GHz Turbo) Socket LGA 170... |

| <b>Model:</b> BX8071514900K<br><b>SKU:</b> 6560418<br> (279)                                                                                        | <b>Model:</b> BX8071514700K<br><b>SKU:</b> 6560420<br> (189)                                                                                        | <b>Model:</b> BX8071514600K<br><b>SKU:</b> 6560423<br> (12)                                                                                         |

# Layered Manufacturing

## Thin Film Processes: MEMS and Microelectronics

53

### Generic Process Flow Diagram

# Layered Manufacturing

Polymer Matrix Composites

# Layered Manufacturing

Thin Film Processes: MEMS and Microelectronics

55

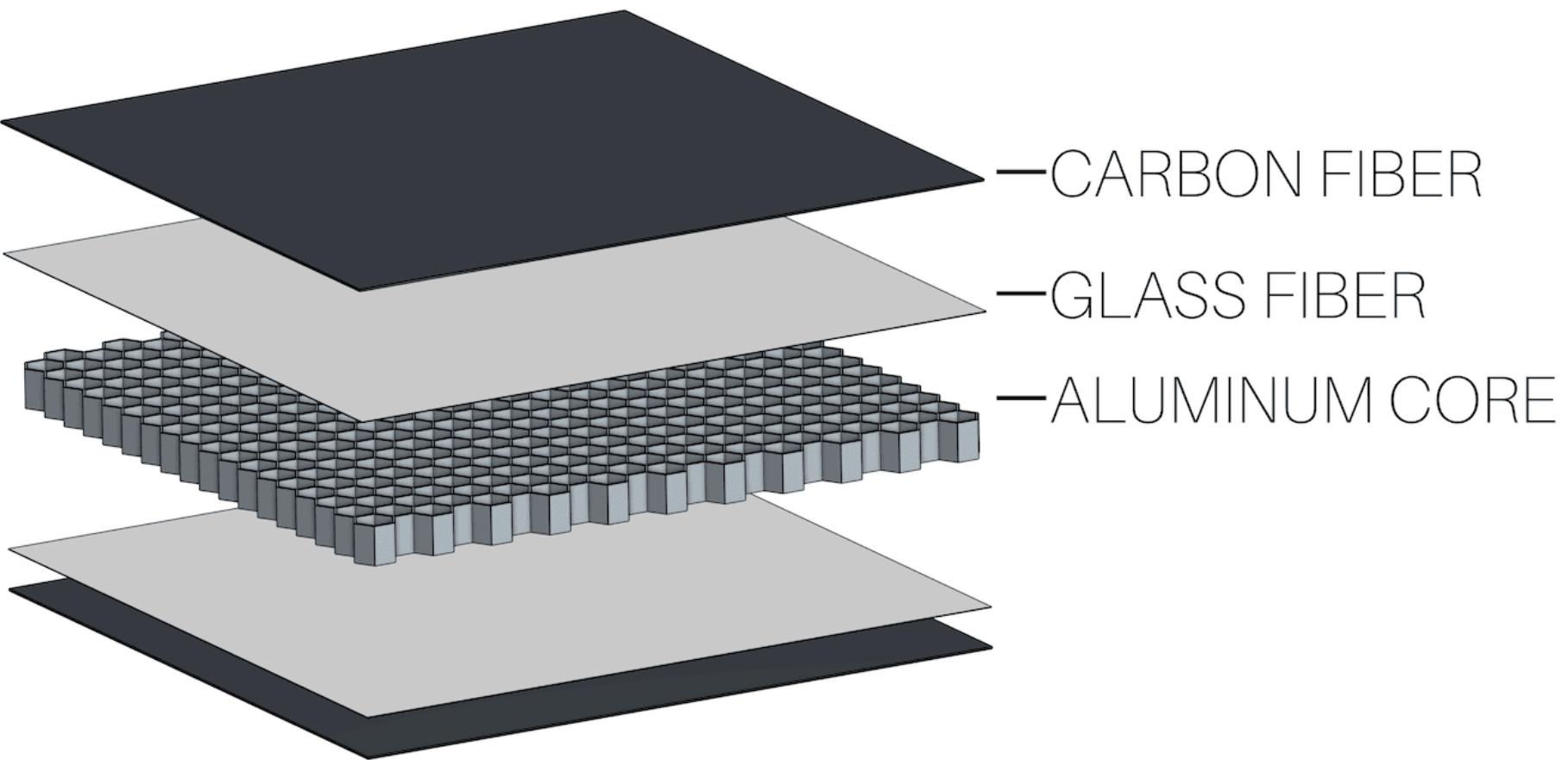

## Polymer Matrix Composites

Sports Technology

Aerospace

# Layered Manufacturing

## Polymer Matrix Composites

56

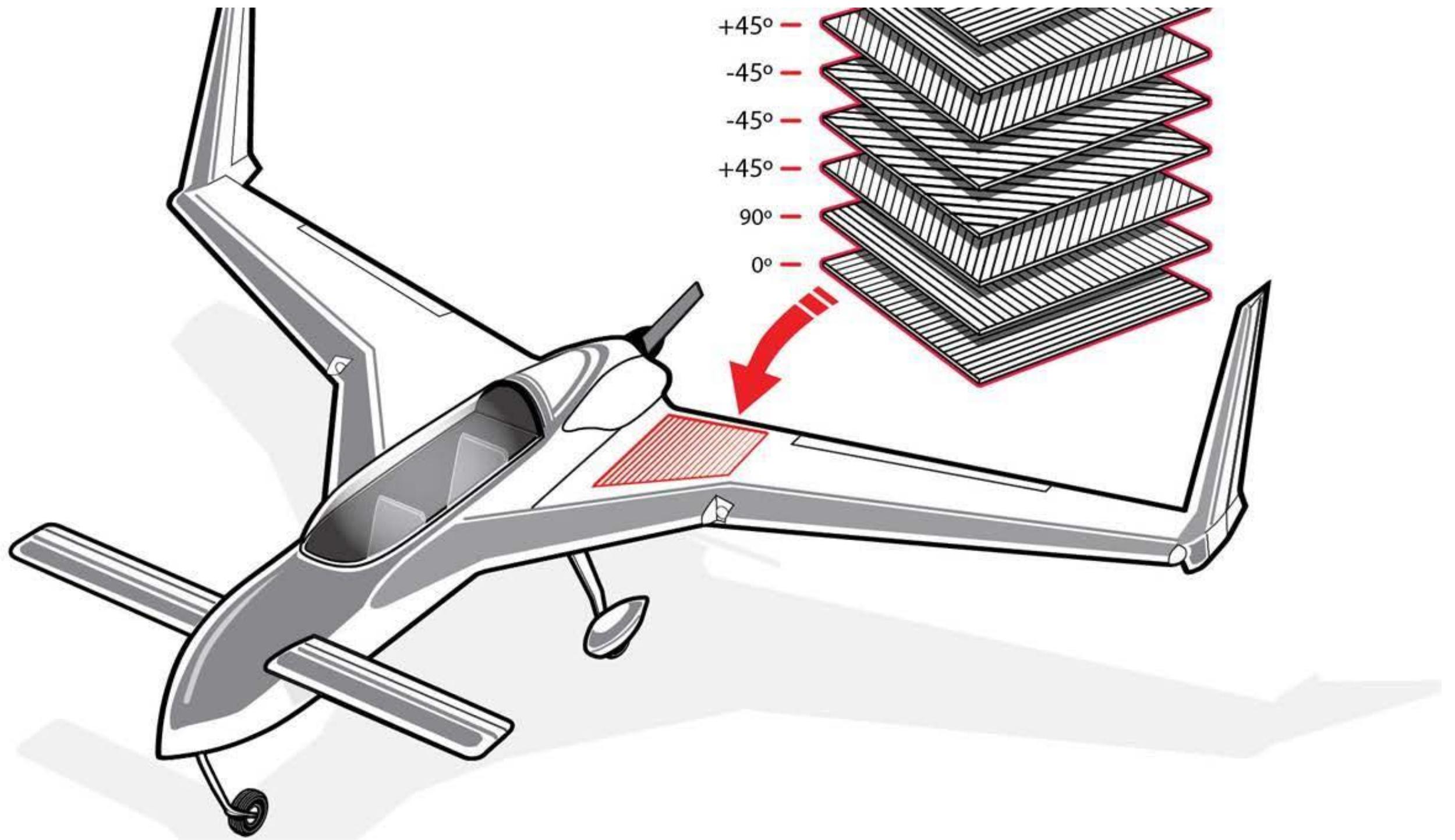

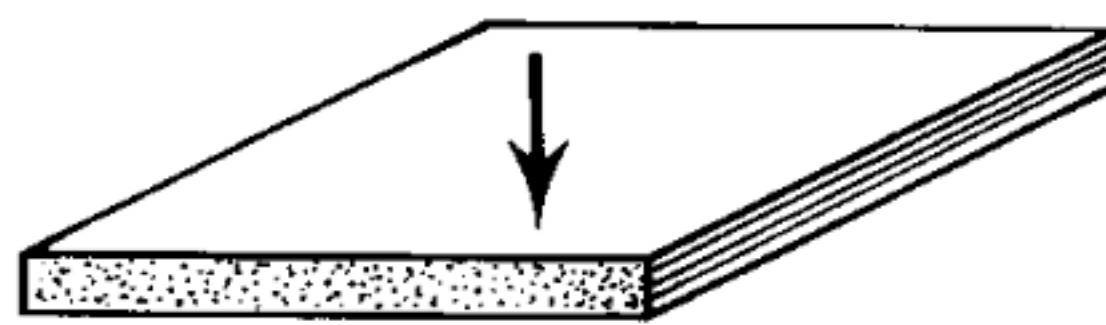

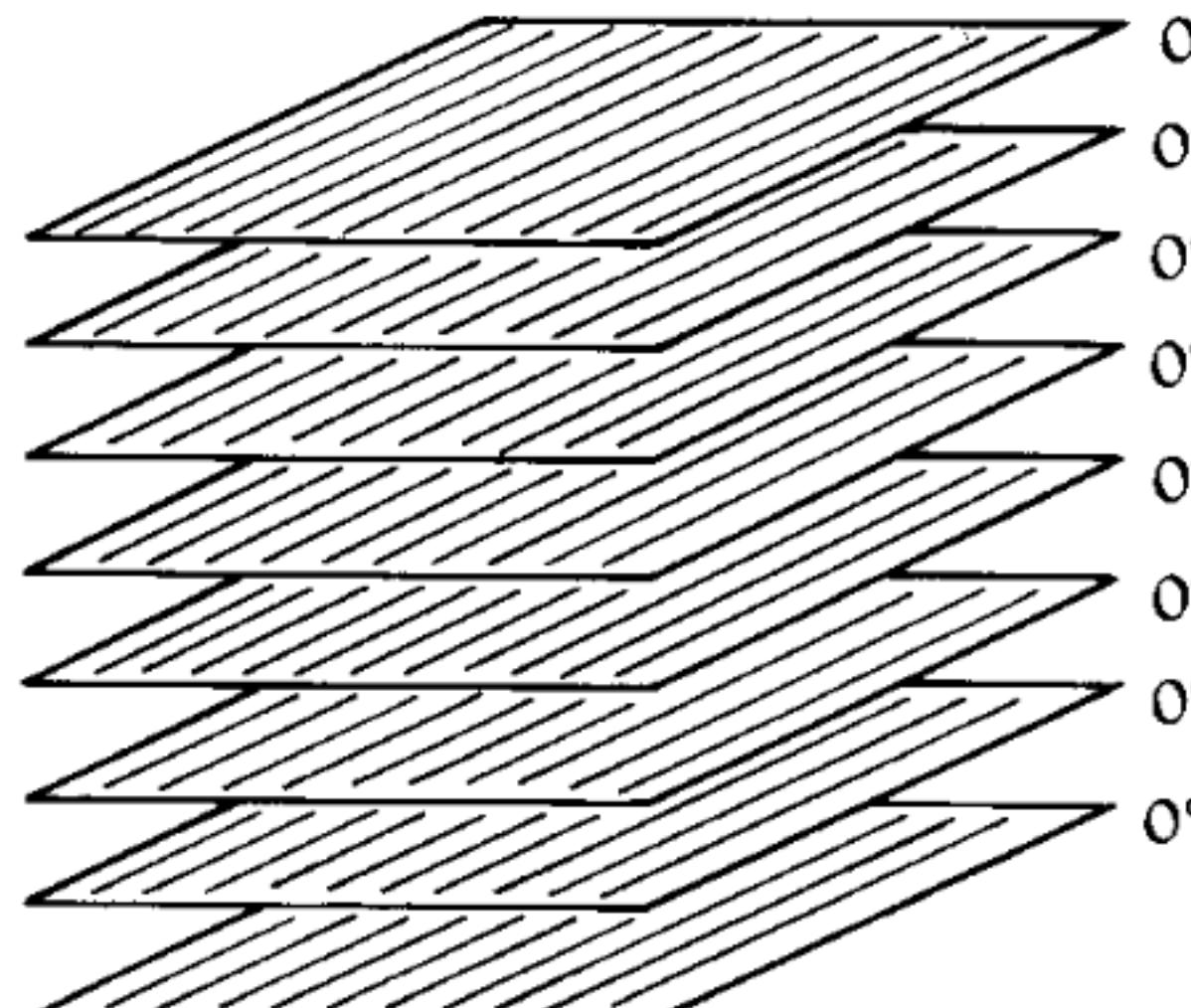

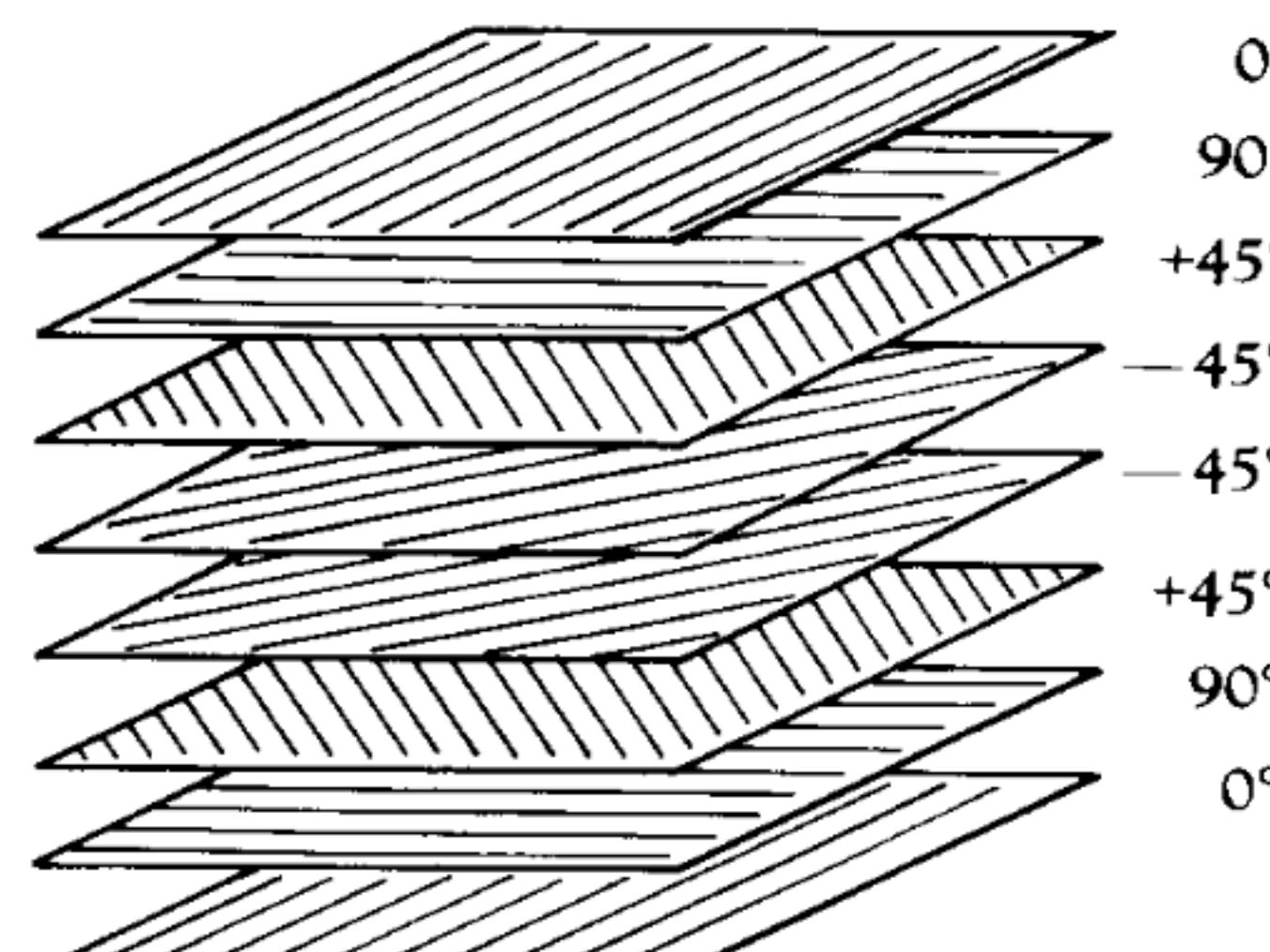

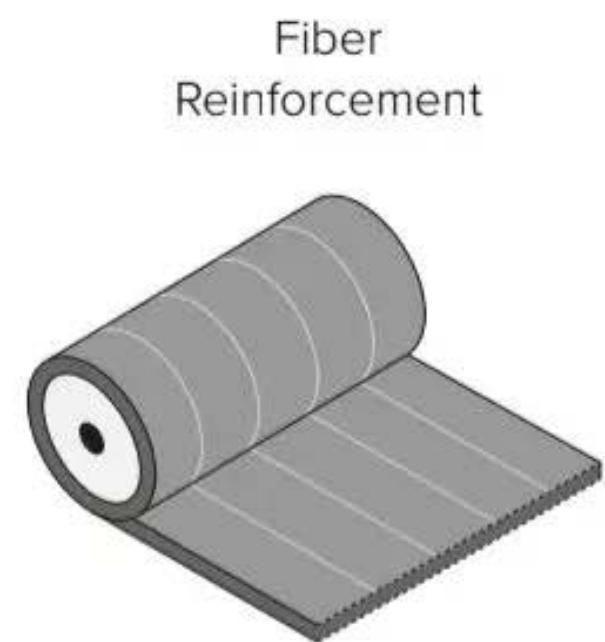

### FRP (Fiber Reinforced Plastic) Composites

Anisotropic

Quasi-isotropic

Fibers: glass, carbon, graphite, boron, kevlar

Matrix: thermosetting resins, thermoplastics

# Layered Manufacturing

## Polymer Matrix Composites

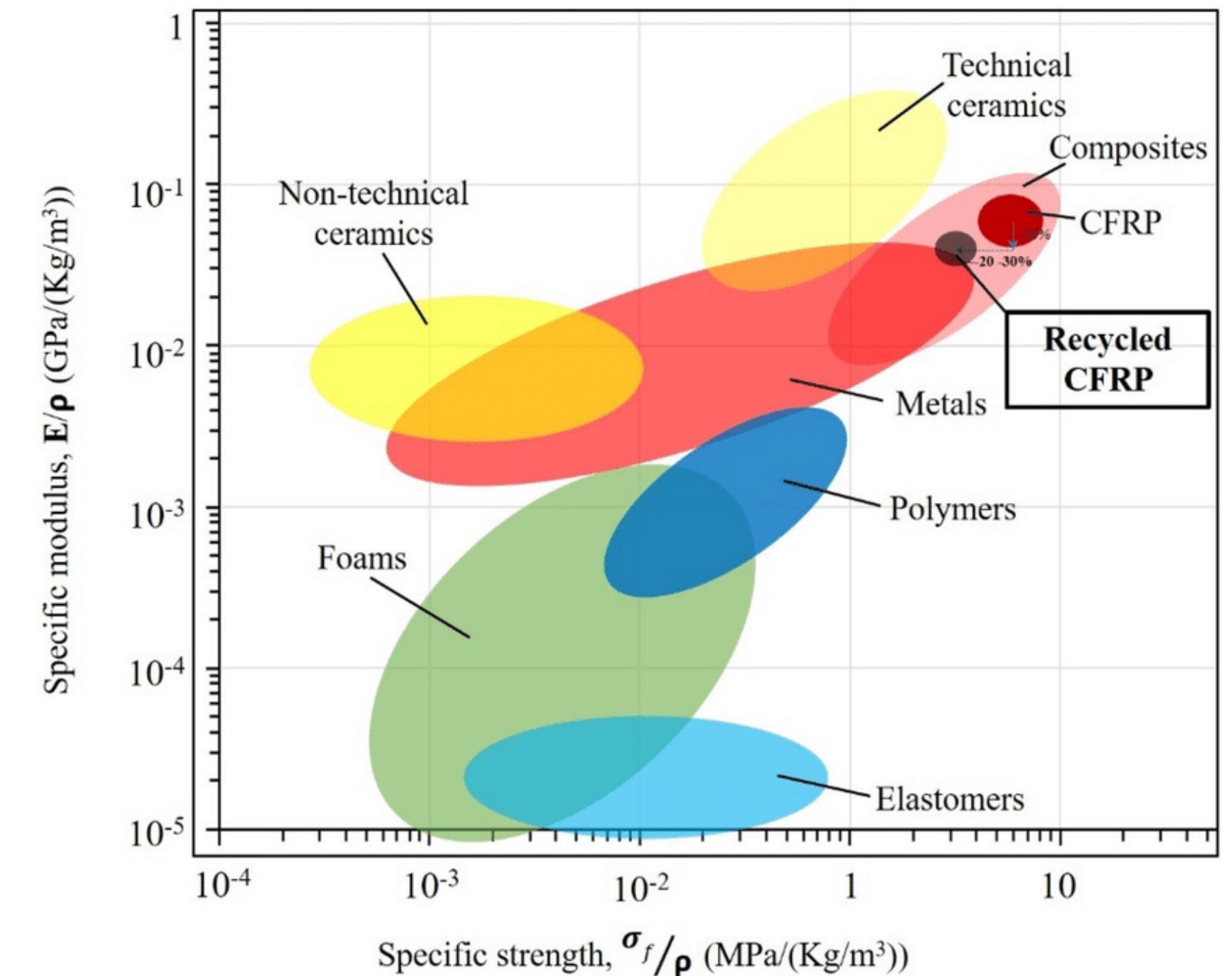

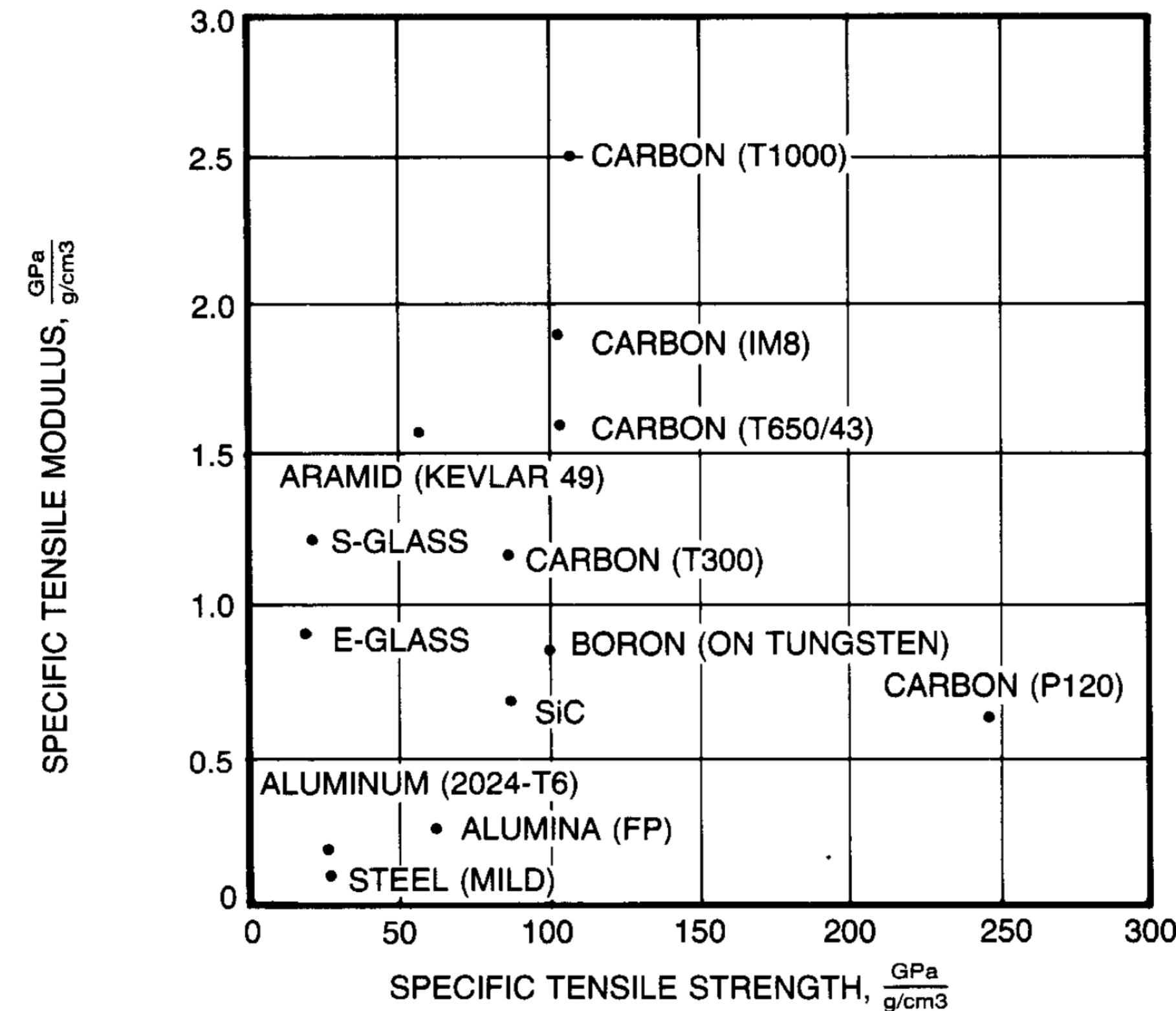

### FRP (Fiber Reinforced Plastic) Composites

### FRP Composite Properties

Comparison: steel, aluminum and composites (65% fiber)

# Layered Manufacturing

## Polymer Matrix Composites

58

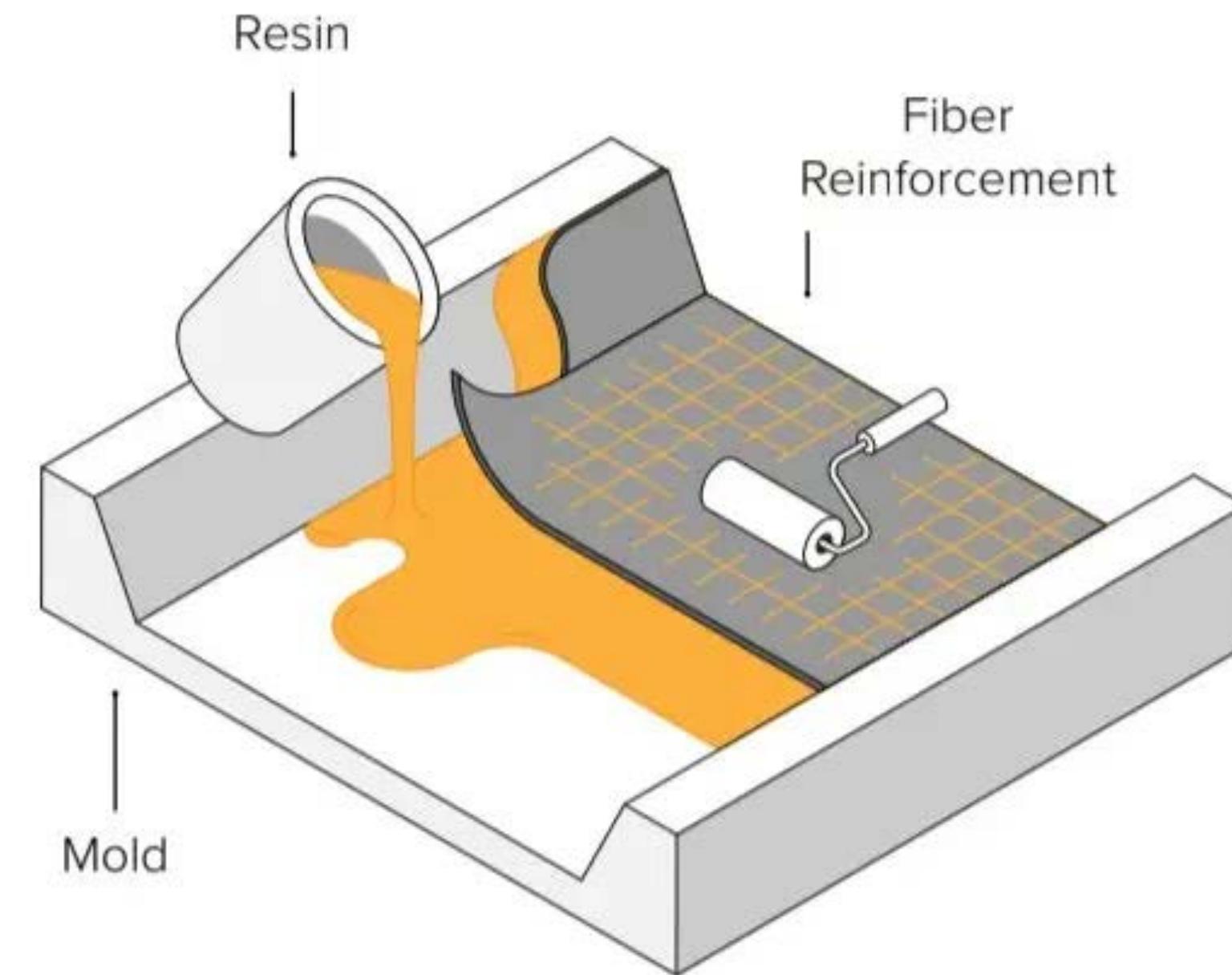

### Hand/Wet Lay Up

# Layered Manufacturing

## Polymer Matrix Composites

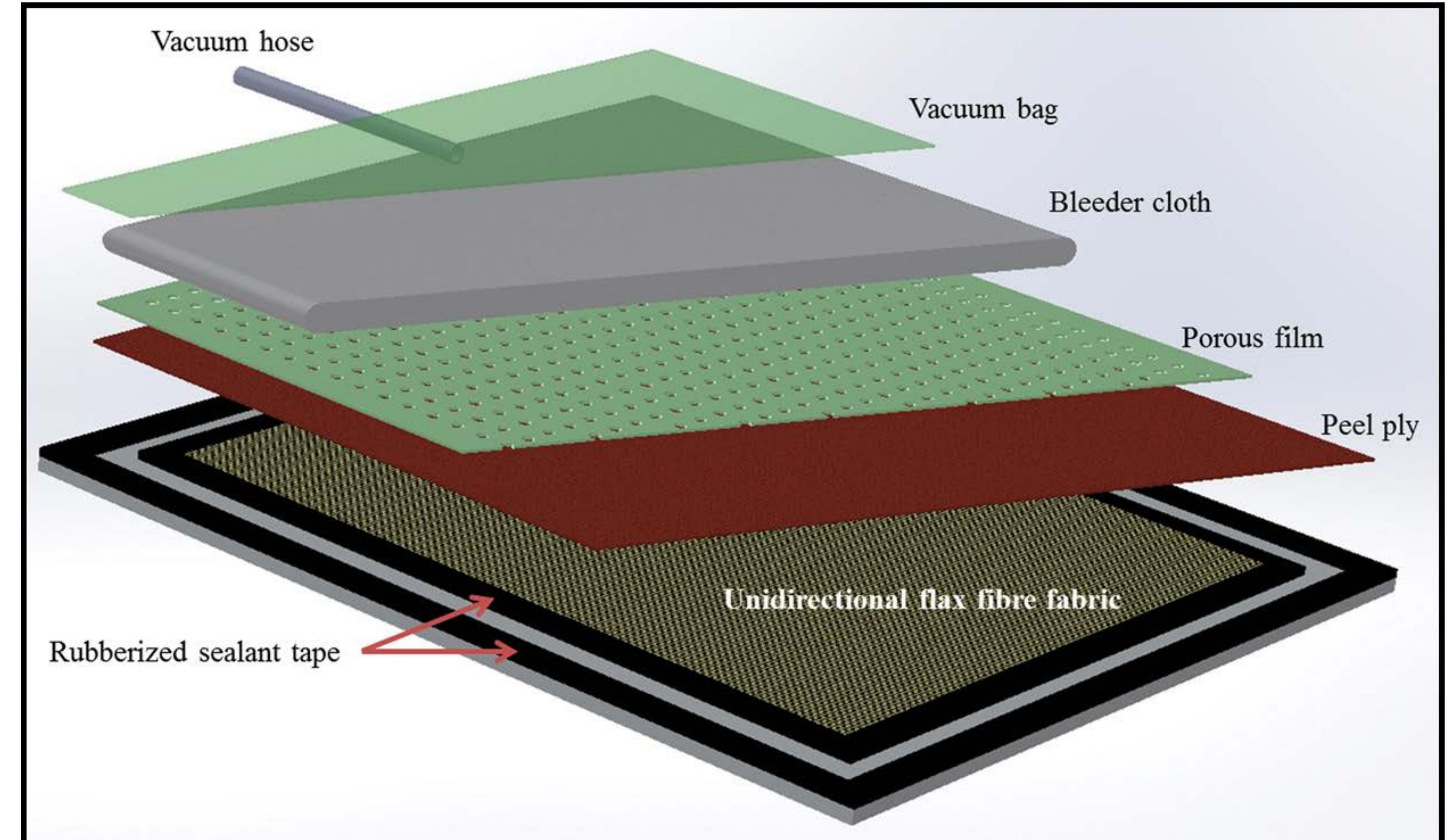

### Vacuum Bag Molding

# Layered Manufacturing

## Polymer Matrix Composites

60

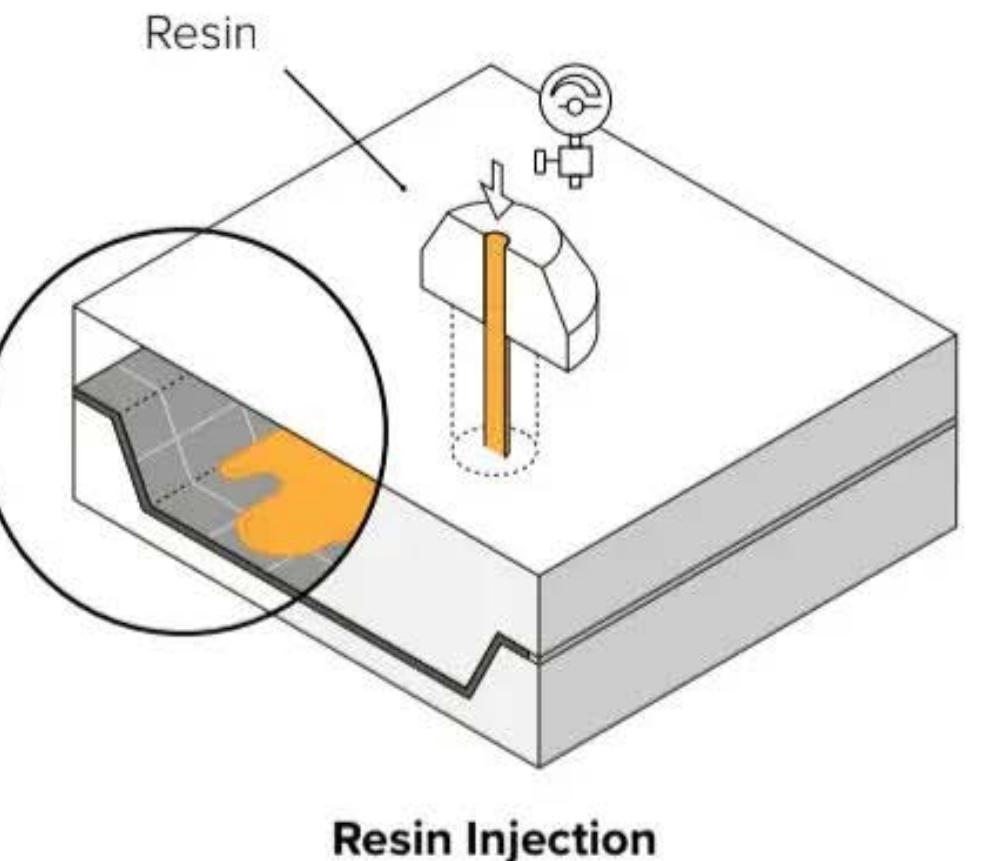

### Resin Transfer Molding

# Layered Manufacturing

## Polymer Matrix Composites

61

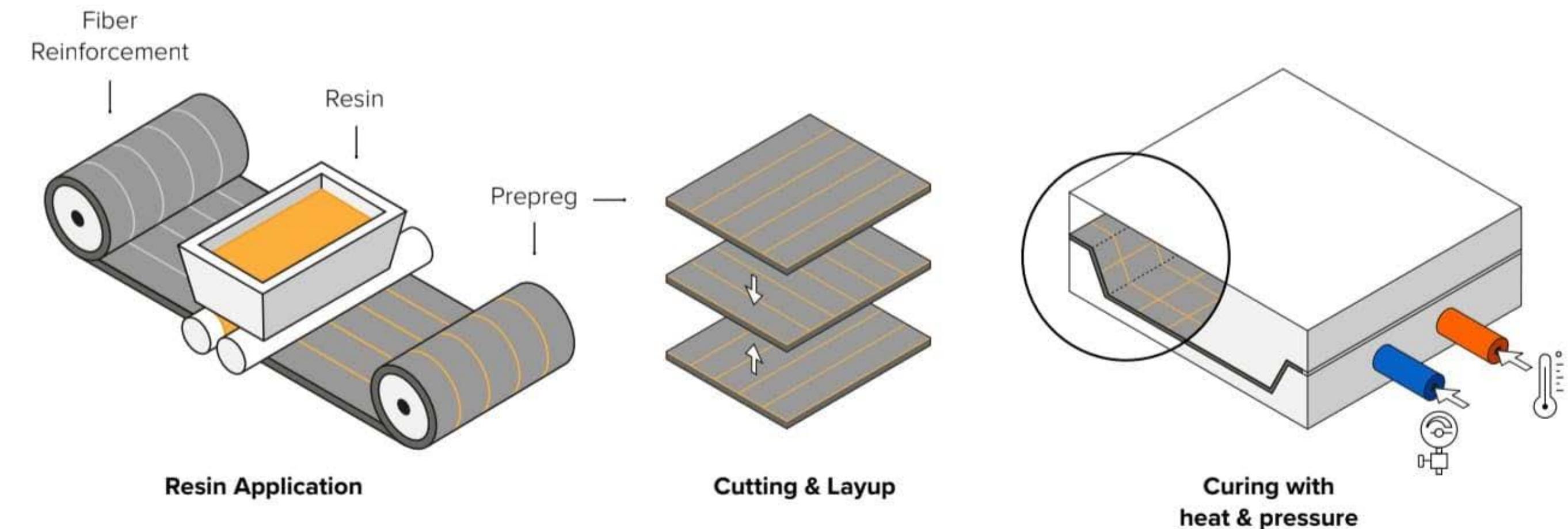

### Pre-Impregnated Sheet Manufacturing

PREPREG PRODUCTION PROCESS

# Layered Manufacturing

## Polymer Matrix Composites

### Autoclave Curing

pressure + temperature = \$

# Layered Manufacturing

## Polymer Matrix Composites

63

### Advantages/Disadvantages

- compressive vs tensile strength

- ability to repair

- cost

# Image Credits

## Slide 1:

© Adobe. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 2:

- Upper left image © Branch Education. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

- The other images © Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 4:

- Left image © Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

- The other images © Envisiontec. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

# Image Credits (cont.)

## Slide 3:

- Left image © Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

- Center image © Make A Gif. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

- Lower right image © Envisiontec. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 5:

© Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 6:

Both images © Branch Education. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

# Image Credits (cont.)

## Slide 7:

© Branch Education. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 8:

- Center image © Springer Nature. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

- Right image © Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 9:

- Left image © Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

- Right image © Cepheiden on [Wikimedia Commons](#). License CC BY-SA. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

# Image Credits (cont.)

## Slide 11:

- Left image © Branch Education. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

- Right image © Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 12:

© Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 14:

Both images © Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 15:

Lower right image © Scanrail. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

# Image Credits (cont.)

## Slide 13:

- Left image © Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

- Upper right image © ePAK International, Inc. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

- Lower right image © wolandmaster. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 16:

© Scanrail. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 18:

Both images © Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

# Image Credits (cont.)

## Slide 19:

Both images on the right hand side © Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 20:

Right image © Samsung Semiconstory. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 23:

© Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 24:

All of images © Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 25:

© Branch Education. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

# Image Credits (cont.)

## Slide 26:

© Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 28:

© ASML. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 29:

© Branch Education. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 30:

© Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 31:

Right image © Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

# Image Credits (cont.)

## Slide 34:

- Lower center image © PVA TePla America. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

- Lower right image © Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 38:

- Center image © Harvey Performance Company, LLC. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

- Right image © John Wiley & Sons, Inc. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 42:

Both images © CVD Equipment Corporation. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

# Image Credits (cont.)

## **Slide 43:**

All of images © Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## **Slide 46:**

Right image © Branch Education. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## **Slide 52:**

© Intel Corporation. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## **Slide 53:**

Lower right image © Scanrail. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## **Slide 54:**

© Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

# Image Credits (cont.)

## Slide 55:

Right image © Steve Karp. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 56:

All of images © Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 58:

- Left image © Core Molding Technologies. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

- Right image © Formlabs. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## Slide 59:

© Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

# Image Credits (cont.)

## **Slide 60:**

Both images © Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## **Slide 61:**

Both images © Source unknown. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## **Slide 62:**

© Piran Advanced Composites. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

## **Slide 63:**

© The Official News Room of Qantas Airways Limited. All rights reserved. This content is excluded from our Creative Commons license. For more information, see <https://ocw.mit.edu/help/faq-fair-use>.

MIT OpenCourseWare

<https://ocw.mit.edu>

2.008 Design and Manufacturing II

Spring 2025

For information about citing these materials or our Terms of Use, visit: <https://ocw.mit.edu/terms>.